# **HP 37717C**

# **Communications Performance Analyzer**

## **Service Manual**

### **SERIAL NUMBERS**

This manual applies directly to modules with serial numbers GB000.

For additional information about serial numbers, see Instruments Covered By Manual in Chapter 1, page 1-8.

HP Part No. 37717-90432 Printed in UK, July 1999

MS-DOS@, Microsoft@ and QuickC@ are U.S. registered trademarks of Microsoft Corporation.

Windows  $^{\mbox{\tiny TM}}$  is trademark of Microsoft Corporation.

@ Copyright Hewlett-Packard Ltd.1999

### Warranty

This Hewlett-Packard product is warranted against defects in materials and workmanship for a period of three years from date of shipment. During the warranty period, Hewlett-Packard Company will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by HP. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

## **Limitation of Warranty**

The foregoing warranty shall not apply to defects resulting from:

- 1 Improper or inadequate maintenance, adjustment, calibration, or operation by Buyer;

- **2** Buyer-supplied software, hardware, interfacing or consumables;

- **3** Unauthorized modification or misuse;

- 4 Operation outside of the environmental and electrical specifications for the product;

- 5 Improper site preparation and maintenance; or

- 6 Customer induced contamination or leaks.

THE WARANTY SET FORTH IS EXCLUSIVE AND NO OTHER WARRANTY, WHETHER WRITTEN OR ORAL, IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

## Limitation of Remedies and Liability

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. IN NO EVENT SHALL HP BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES (INCLUDING LOSS OF PROFITS) WHETHER BASED ON CONTRACT, TORT OR ANY OTHER LEGAL THEORY.

## **Responsibilities of the Customer**

The customer shall provide:

- 1 Access to the products during the specified periods of coverage to perform maintenance.

- 2 Adequate working space around the products for servicing by Hewlett-Packard personnel.

- 3 Access to and use of all information and facilities determined necessary by Hewlett-Packard to service and/or maintain the products. (Insofar as these items may contain proprietary or classified information, the customer shall assume full responsibility for safeguarding and protection from wrongful use.)

- **4** Routine operator maintenance and cleaning as specified in the Hewlett-Packard Operating and Service Manuals.

- **5** Consumables such as paper, disks, magnetic tapes, ribbons, inks, pens, gases, solvents, columns, syringes, lamps, septa, needles, filters, frits, fuses, seals, detector flow cell windows, etc.

### Certification

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility and to the calibration facilities of other International Standards Organization members!

#### Assistance

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

#### **Notice**

The information contained in this document is subject to change without notice.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of the manufacture, Hewlett-Packard Ltd.

## **Restricted Rights Legend**

Use, duplication, or disclosure by the government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause at 52.227-7013. Hewlett-Packard Company; 3000 Hanover Street; Palo Alto, California 94304.

## **Statement of Compliance**

This instrument has been designed and tested in accordance with IEC Publication 1010-1 + A1:1992 Safety requirements for Electrical Equipment for Measurement, Control and Laboratory Use, and has been supplied in a safe condition. The instruction documentation contains information and warnings which must be followed by the user to ensure safe operation and to maintain the instrument in a safe condition.

## **Electromagnetic Compatibility (EMC) Information**

This product has been designed to meet the protection requirements of the European Communities Electromagnetic Compatibility (EMC) directive 89/336/EEC. In order to preserve the EMC performance of the product, any cable which becomes worn or damaged must be replaced with the same type and specification.

### **Safety Information**

The following general safety precautions must be observed during all phases of operation, service, and repair of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument. Hewlett-Packard Company assumes no liability for the customer's failure to comply with these requirements.

#### General

This is a Safety Class I instrument (provided with terminal for protective earthing) and has been manufactured and tested according to international safety standards.

**DO NOT** operate the product in an explosive atmosphere or in the presence of flammable gasses or fumes.

**DO NOT** use repaired fuses or short-circuited fuseholders: For continued protection against fire, replace the line fuse(s) only with fuse(s) of the same voltage and current rating and type.

**DO NOT** perform procedures involving cover or shield removal unless you are qualified to do so: Operating personnel must not remove equipment covers or shields. Procedures involving the removal of covers and shields are for use by service-trained personnel only.

**DO NOT** service or adjust alone: Under certain conditions, dangerous voltages may exist even with the equipment switched off. To avoid dangerous electrical shock, service personnel must not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

**DO NOT** operate damaged equipment: Whenever it is possible that the safety protection features built into this product have been impaired, either through physical damage, excessive moisture, or any other reason, REMOVE POWER and do not use the product until safe operation can be verified by service-trained personnel. If necessary, return the product to a Hewlett-Packard Sales and Service Office for service and repair to ensure the safety features are maintained.

**DO NOT** substitute parts or modify equipment: Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to a Hewlett-Packard Sales and Service Office for service and repair to ensure the safety features are maintained.

## Safety Symbols

The following symbols on the instrument and in the manual indicate precautions which must be taken to maintain safe operation of the instrument.

| Safety Symbols |                                                                                                                                                                                                                                                                           |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| $\triangle$    | The Instruction Documentation Symbol. The product is marked with this symbol when it is necessary for the user to refer to the instructions in the supplied documentation.                                                                                                |  |  |  |  |

| <b>=</b>       | Indicates the field wiring terminal that must be connected to earth ground before operating the equipment - protects against electrical shock in case of fault.                                                                                                           |  |  |  |  |

| → or ⊥         | Frame or chassis ground terminal - typically connects to the equipment's metal frame.                                                                                                                                                                                     |  |  |  |  |

| $\sim$         | Alternating current (AC)                                                                                                                                                                                                                                                  |  |  |  |  |

| ===            | Direct current (DC)                                                                                                                                                                                                                                                       |  |  |  |  |

| 7              | Indicates hazardous voltages                                                                                                                                                                                                                                              |  |  |  |  |

| WARNING        | Warning denotes a hazard. It calls attention to a procedure, which if not correctly performed or adhered to could result in injury or loss of life. Do not proceed beyond a warning note until the indicated conditions are fully understood and met.                     |  |  |  |  |

| CAUTION        | Caution denotes a hazard. It calls attention to a procedure, which if not correctly performed or adhered to could result in damage to or destruction of the instrument. Do not proceed beyond a warning note until the indicated conditions are fully understood and met. |  |  |  |  |

| CE             | The CE mark shows that the product complies with all relevant European legal Directives accompanied by a year, it's when the design was proven).                                                                                                                          |  |  |  |  |

| ISM 1-A        | This is a symbol of an Industrial Scientific and Medical Group 1 Class A product.                                                                                                                                                                                         |  |  |  |  |

| <b>(1)</b>     | The CSA mark is a registered trademark of the Canadian Standards Association.                                                                                                                                                                                             |  |  |  |  |

| EN 60825 1991  | Indicates that a laser is fitted. The user must refer to the manual for specific Warning or Caution information to avoid personal injury or damage to the product.                                                                                                        |  |  |  |  |

### **Laser Safety**

To avoid hazardous exposure to laser radiation, it is recommended that the following practices are observed during system operation:

- ALWAYS DEACTIVATE THE LASER BEFORE CONNECTING OR DISCONNECTING OPTICAL CABLES.

- When connecting or disconnecting optical cables between the module and device-under-test, observe the connection sequences given below:

**Connecting:** Connect the optical cable to the input of the device-under-test **before**

connecting to the module's Optical Out connector.

**Disconnecting:** Disconnect the optical cable from the module's *Optical Out* connector **before**

disconnecting from the device-under-test. Always ensure the shutter (if fitted)

closes properly and covers the laser aperture.

- NEVER examine or stare into the open end of a broken, severed, or disconnected optical cable when it is connected to the module's *Optical Out* connector.

- Arrange for service-trained personnel, who are aware of the hazards involved, to repair optical cables.

#### CAUTION

- 1. Use of controls or adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

- 2. Always leave the fibreoptic connector dust caps on each connector when not in use. Before connection is made, *always* clean the connector ferrule tip with acetone or alcohol and a cotton swab. Dry the connector with compressed air. Failure to maintain cleanliness of connectors is liable to cause excessive insertion loss.

General viii Safety Symbols ix Laser Safety x

### General Information 1-1

Safety Considerations 1-1

Manual Safety Markings 1-1

Instrument Safety Markings 1-2

Laser Safety 1-2

Laser Warning Symbols 1-3

ESD Precautions 1-6

Electromagnetic Compatibility 1-6

Radiated Emissions 1-6

Electrostatic Discharge 1-6

Operators Maintenance 1-7

Cleaning 1-7

Instruments Covered By Manual 1-8

#### Installation 2-1

**Initial Inspection 2-1**

Preparation for Use 2-2

Power Requirements 2-2

Operators Maintenance 2-3

Fuse Replacement 2-3

Line Voltage Selector Switch 2-3

Hewlett-Packard Interface Bus 2-3

**HP-IB Address Selection 2-4**

Operating Environment 2-5

Storage and Shipment 2-5

Repackaging for Shipment 2-5

## Adjustments 3-1

Introduction 3-1

Safety Considerations 3-1

Requirements for Adjustments 3-1

Adjustment Type 3-2

List of Soft Adjustments 3-2

List of Adjustable Components 3-2

Warm-Up Time 3-5

Adjustment Sequence 3-6

Access to Adjustable Components 3-6

Equipment Required 3-6

Recall Default Settings 3-7

10 MHz Reference Clock Frequency and VCXO 3-8

Unstructured PDH Transmitter (Option UKK) 3-10

Unstructured PDH Receiver (Option UKK) 3-13

SDH Transmitter (Options US1 and AIT) 3-17

SDH Receiver (Option AIT) 3-20

External Clock (Option A1T) 3-22

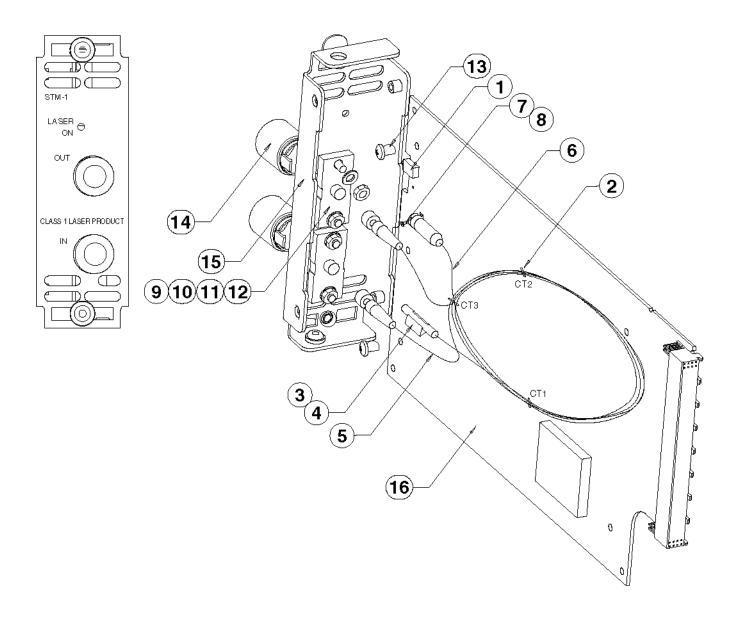

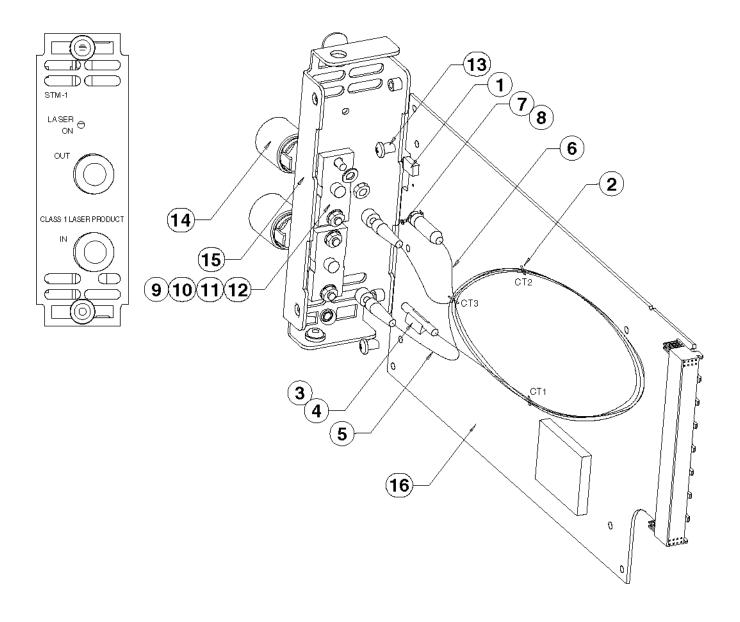

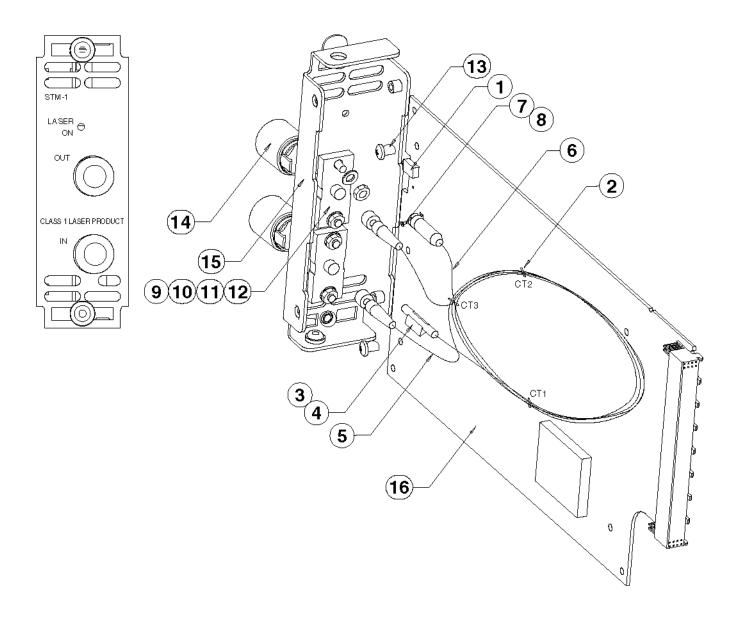

1310 nm STM-1 Optical Transmitter (Option UH1 Only) 3-25

1310 nm STM1/4 Optical Transmitter (Option USN and UKT) 3-27

1550 nm STM1/4 Optical Transmitter (Option USN Only) 3-29

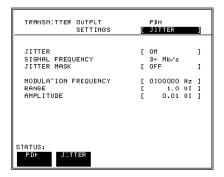

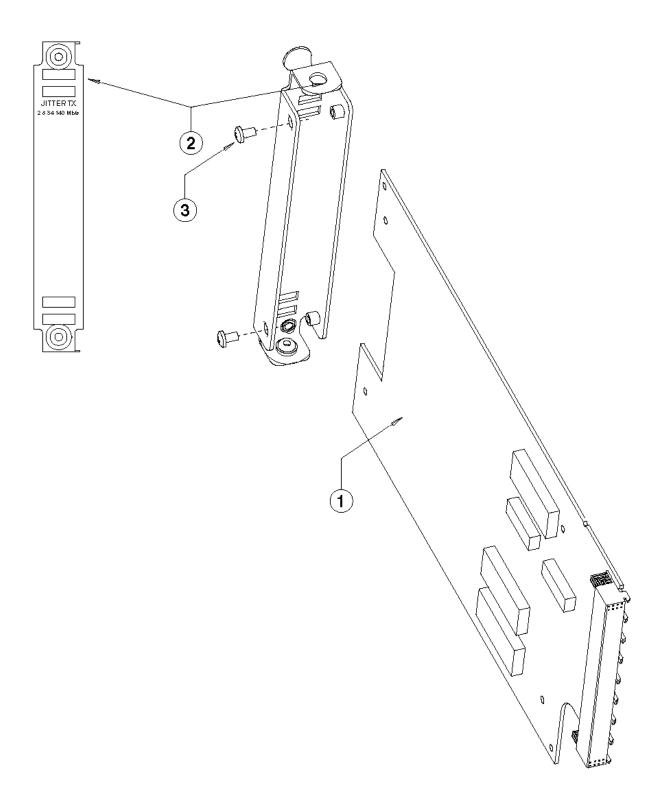

Jitter Transmitter (Option UHK) 3-31

Jitter Generator (Options A3K, 140) 3-40

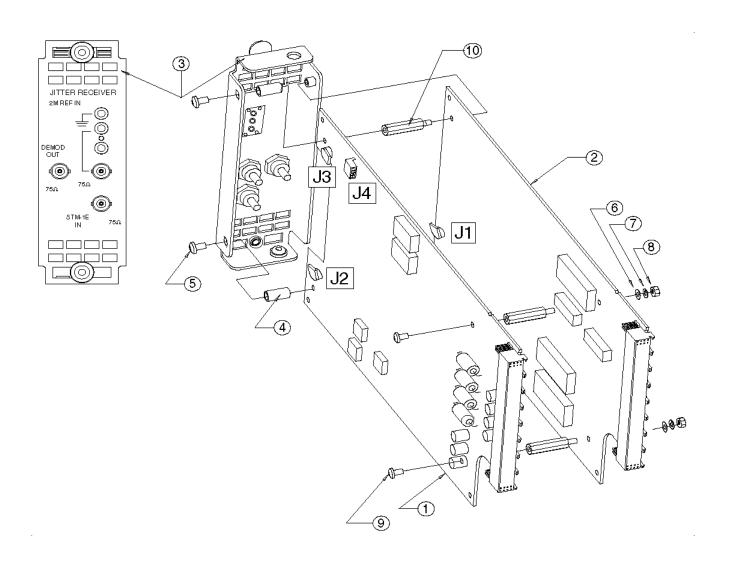

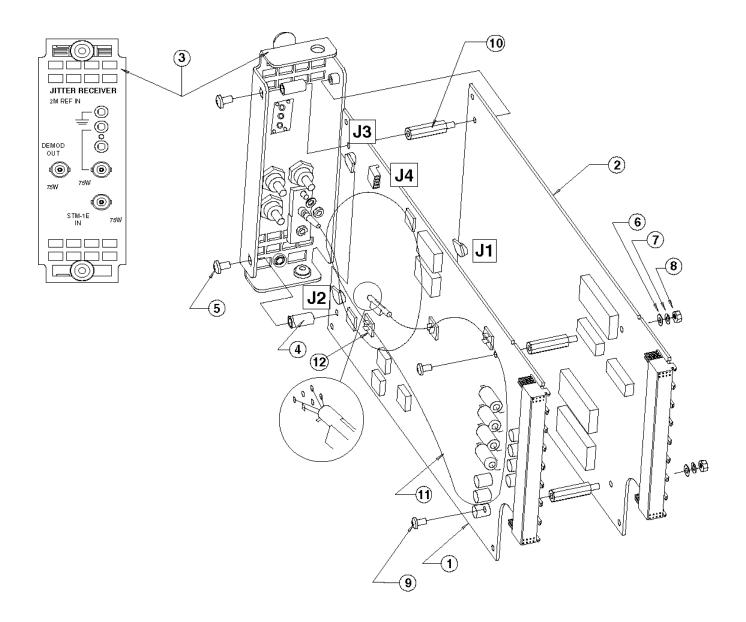

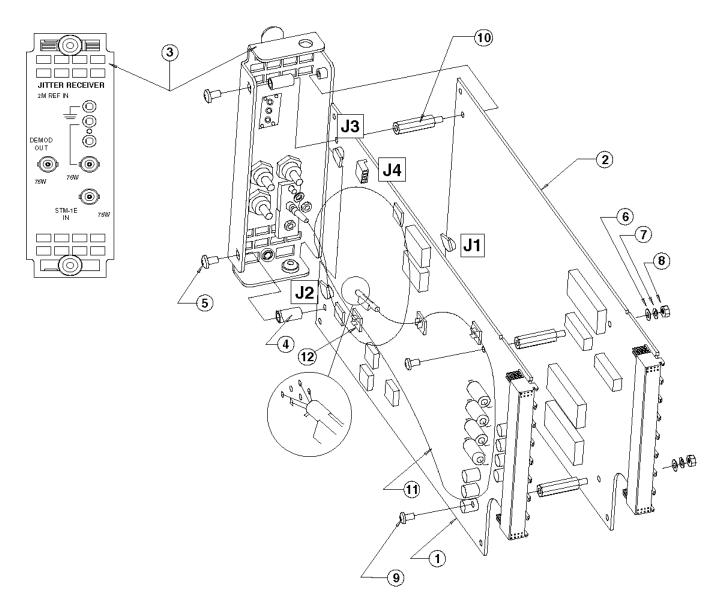

Jitter Receiver (Option UHN) 3-44

STM Line Jitter Receiver (Options A3L and A3M) 3-50

STM Line Jitter Receiver (Options AIM, AIN and AIP) 3-54

STM 10 Clock Recovery (Options A1N and A1P) 3-57

STM 40 Clock Recovery (Option AIP) 3-59

Jitter Receiver (Options A3L, A3M, A3N, A3P, A3V and A3W) 3-61

Structured PDH Transmitter (Options UKJ, USA) 3-67

Structured PDH Receiver (Options UKJ, USA) 3-71

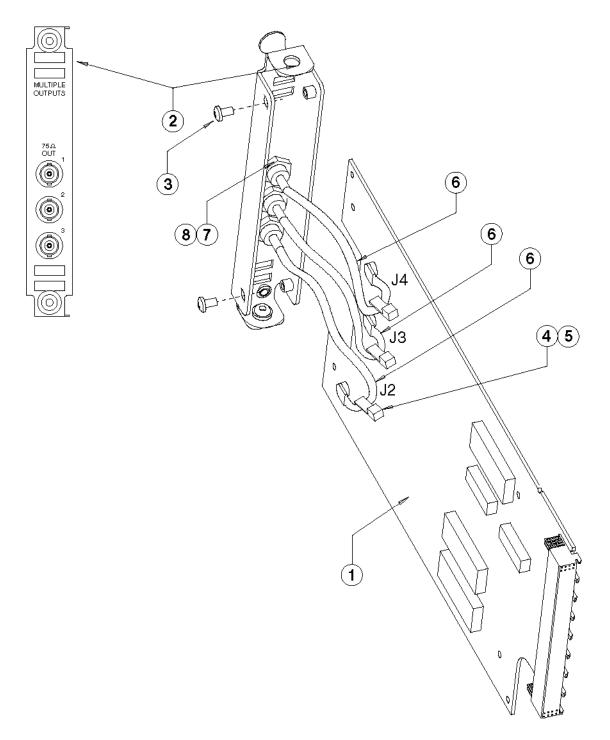

Multiple Outputs (Option UHC) 3-74

ATM Cell Layer Transmitter (Option UKZ) 3-77

ATM Cell Layer Receiver (Option UKZ) 3-83

Binary Interface (Option UH3) 3-88

STM Clock (Option A3R) 3-94

**SDH** (Option A3R) 3-101

## Replaceable Parts 4-1

**Introduction 4-1**

Exchange Program 4-1

Ordering Information 4-1

#### Service 5-1

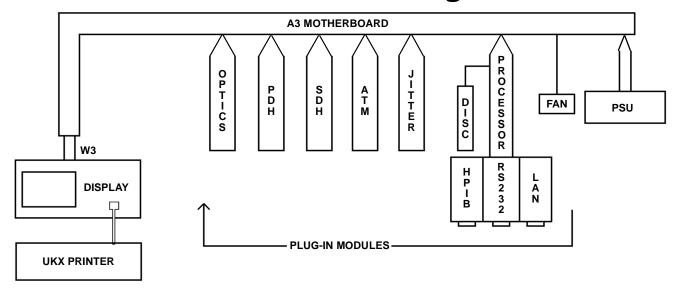

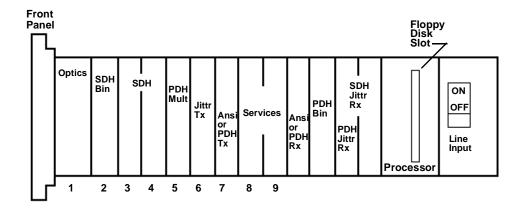

Theory of Operation 5-1

Display/Keyboard 5-2

In Lid Printer 5-2

Self Tests 5-2

#### General Information 5-3

Safety Considerations 5-3

Anti-static Precautions 5-3

Repair Strategy 5-4

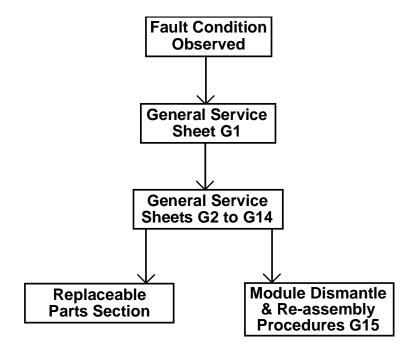

Troubleshooting 5-4

Built-in Service Features 5-5

Power -on Checks 5-5

Self-Test 5-5

Calibration Routines 5-5

Module Debug Page 5-5

Debug Function Page 5-6

Test and Probe Points 5-6

Extender Cards 5-6

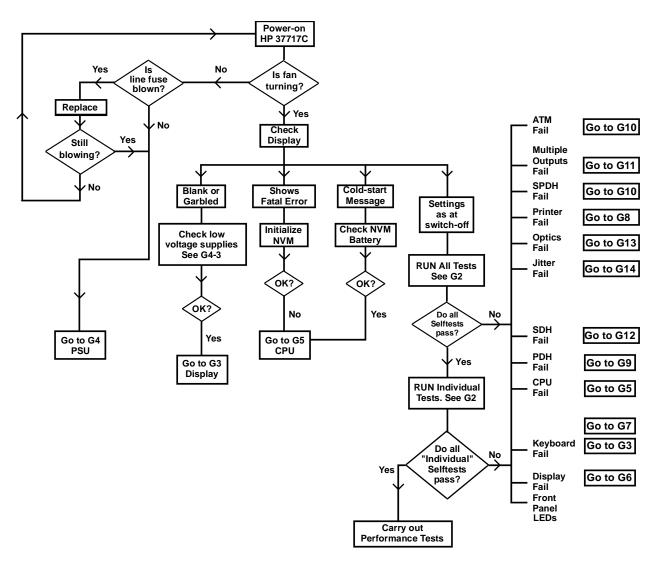

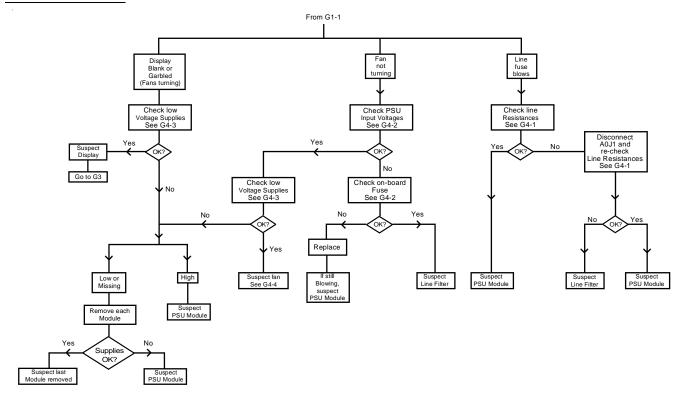

General Service Sheet G1 - Troubleshooting Entry 5-7

General Service Sheet G2 - Self Test 5-9

SERVICE NOTE 37717C-10 B-31 SERVICE NOTE 37717C-11 B-33 SERVICE NOTE 37717C-12 B-35

Selftest Notes 5-13 Diagnostic Tests 5-13 Self Test Fail Numbers 5-15 Service Sheet G3 - Colour Display 5-91 Service Sheet G4 - Power Supply 5-93 Service Sheet G5 - Processor (CPU) 5-97 Fatal Errors 5-101 Service Sheet G6 - Front Panel LEDS 5-107 Service Sheet G7 - Front Panel Membrane Keyboard 5-109 Service Sheet G8 - Printer 5-111 Service Sheet G9 - Unstructured PDH Module 5-113 Service Sheet G10 - Structured PDH Modules and ATM 5-117 Service Sheet G11 - PDH Multiple Outputs Module 5-127 Service Sheet G12 - SDH Module 5-129 Service Sheet G13 - Optical Interface Module (Options UH1, 130 and 131) 5-159 Service Sheet G14 - (Options USN, UKT, 130 and 131) 5-165 Service Sheet G15 - Jitter Transmitter and Receiver Modules 5-195 General Service Sheet G16 - Dismantling and Re-assembly Procedures 5-215 Removing Board Assemblies from a Module 5-218 Front Panel Assembly 5-241 PSU Module 5-242 Line Module 5-243 Cooling Fans 5-243 Default settings A-1 SERVICE NOTE 37717C-01A B-1 **SERVICE NOTE 37717C-02 B-5 SERVICE NOTE 37717C-03 B-6** SERVICE NOTE 37717C-04 B-11 **SERVICE NOTE 37717C-05 B-16 SERVICE NOTE 37717C-06 B-20 SERVICE NOTE 37717C-07 B-23** SERVICE NOTE 37717C-08 B-28 **SERVICE NOTE 37717C-09 B-29**

## **General Information**

This section contains general information concerning the HP 37717C Communications Performance Analyzer.

**Safety Considerations**

**Electromagnetic Compatibility**

**Operators Maintenance**

**Instruments Covered by Manual**

**Options**

Accessories

## **Safety Considerations**

The HP 37717C Communications Performance Analyzer is a Safety Class 1 (IEC) product (provided with a protective earthling ground incorporated in the power cord).

This instrument has been designed and tested in accordance with IEC Publication 1010-1 (1990) with Amendment 1 (1992), Safety Requirements for Electronic Measuring Apparatus, and has been supplied in a safe condition. The instruction documentation contains information and warnings which must be followed by the user to ensure safe operation and to maintain the instrument in a safe condition.

#### **Manual Safety Markings**

#### WARNING

THE WARNING SIGN DENOTES A HAZARD TO THE OPERATOR. IT CALLS ATTENTION TO A PROCEDURE, PRACTICE, OR THE LIKE, WHICH IF NOT CORRECTLY PERFORMED OR ADHERED TO, COULD RESULT IN INJURY OR LOSS OF LIFE. DO NOT PROCEED BEYOND A WARNING SIGN UNTIL THE INDICATED CONDITIONS ARE FULLY UNDERSTOOD AND MET.

#### CAUTION

The CAUTION sign denotes a hazard to the instrument. It calls attention to an operating or maintenance procedure, practice, or the like, which if not correctly performed or adhered to, could result in damage to or destruction of part or all of the instrument. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

### **Instrument Safety Markings**

**Refer To Manual**: This symbol on the instrument means the user must refer to the Calibration and Service Manuals to protect the instrument from damage.

Laser Warning Label - Hazard Symbol

#### WARNING

NO OPERATOR SERVICEABLE PARTS INSIDE. REFER SERVICING TO QUALIFIED PERSONNEL. TO PREVENT ELECTRICAL SHOCK DO NOT REMOVE COVERS.

### **Laser Safety**

#### WARNING

To prevent personal injury, avoid use which may be hazardous to others, and maintain the module in a safe condition, ensure the information given below is reviewed before operating the module.

#### **Laser Product Classification**

All Options UH1, UH2, URU, USN and UKT, 130, 131 are classified as Class I (non-hazardous) laser product in the USA which complies with the United States Food and Drug Administration (FDA) Standard 21 CFR Ch.1 1040.10. Options UH1, UH2 and UKT are classified as Class 1 (non-hazardous) laser products in Europe which complies with EN 60825-1 (1994).

Options URU and USN are classified as a Class 3A laser product in Europe, which complies with EN 60825-1 (1994).

Laser classification is based on the ability of the optical beam to cause biological damage to the eye or skin. The EN 60825-1 (1994) definition of Class 3A is:

"Any laser product which permits human access to laser radiation in excess of the accessible emission limits of Class I and Class 2 as applicable, but which does not permit human access to laser radiation in excess of the accessible emissions of Class 3A and Class 3B (respectively) for any emission duration and wavelength."

Options URU and USN fall into this category, under the EN 60825-1 (1994) (European) standard, because they have a maximum output power of 19.5 me (under fault conditions), with a wavelength of 1550 nm.

To avoid hazardous exposure to laser radiation, it is recommended that the following practices are observed during system operation:

#### ALWAYS DEACTIVATE THE LASER BEFORE CONNECTING OR DISCONNECTING OPTICAL CABLES.

• When connecting or disconnecting optical cables between the module and device-under-test, observe the connection sequences given below.

**Connecting:** Connect the optical cable to the input of the device-under-test **before** connecting

to the module's Optical Out connector.

**Disconnecting:** Disconnect the optical cable from the module's *Optical Out* connector **before** dis-

connecting from the device-under-test. Always ensure the shutter closes properly

and covers the laser aperture.

- NEVER examine or stare into the open end of a broken, severed, or disconnected optical cable when it is connected to the module's *Optical Out* connector.

- Arrange for service-trained personnel, who are aware of the hazards involved, to repair optical cables.

#### CAUTION

Use of controls or adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

### **Laser Warning Symbols**

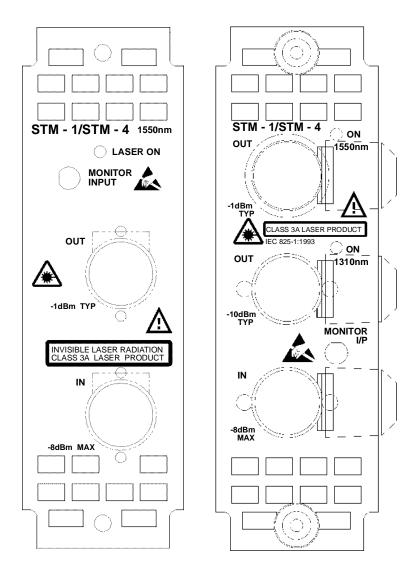

Options UH1, UH2 and UKT optical module's front panel contains the following label:

CLASS 1 LASER PRODUCT

This label indicates that the radiant energy present in this instrument is non-hazardous.

**Option USN** optical module's front panel contains the following labels:

**CLASS 3A LASER PRODUCT**

CLASS 3A: Lasers which are safe for viewing with the unaided eye. For laser emitting in the wavelength range from 400 nm to 700 nm, protection is afforded by aversion responses including the blink reflex. For other wavelengths the hazard to the unaided eye is no greater than for Class I. Direct antiurban viewing of Class 3A lasers with optical aids (e.g. binoculars, telescopes, microscopes) may be hazardous.

#### **Swedish and Finnish Labels**

VARO! NÄKYMÄTONTÄ LASERSÄTEILYLLE ALÄ TUIJOTA SÄTEESEEN ÄLÄKÄ KATSO SITÄ OPTISEN LAITTEEN LÄPI LUOKAN 3A LASERLAITE

VARNING - OSYNLIG LASERSTRÅLNING STIRRA ET IN I STRÅLEN OCH BETRAKTA EJ STRÅLEN GENOM OPTISKT INSTRUMENT KLASS 3A LASER APPARAT

VARNING - OSYNLIG LASERSTRÅLNING STIRRA ET IN I STRÅLEN OCH BETRAKTA EJ STRÅLEN MED OPTISKA INSTRUMENT CLASS 3A LASER PRODUCT

### **Location of Laser Apertures**

Figure 1-1 Option 131 Option USN

General Information ESD Precautions

## **ESD Precautions**

#### CAUTION

The module contains components sensitive to electrostatic discharge. To prevent component damage, carefully follow the handling precautions presented below.

The smallest static voltage most people can feel is about 3500 volts. It takes less than one tenth of that (about 300 volts) to destroy or severely damage static sensitive circuits. Often, static damage does not immediately cause a malfunction but significantly reduces the component's life. Adhering to the following precautions will reduce the risk of static discharge damage.

- Keep the module in its conductive storage box when not installed in the Mainframe. Save the box for future storage of the module.

- Before handling the module, select a work area where potential static sources are minimized. Avoid working in carpeted areas and non-conductive chairs. Keep body movement to a minimum. Hewlett-Packard recommends that you use a controlled static workstation.

- Handle the module by its front-panel. Avoid touching any components or edge connectors. When you install the module, keep one hand in contact with the protective bag as you pick up the module with your other hand. Then, before installing the module, make contact with the metal surface of the Mainframe with your free hand to bring you, the module, and the mainframe to the same static potential. This also applies whenever you connect/disconnect cables on the front-panel.

#### CAUTION

The connectors on the front-panel of the module remain susceptible to ESD damage while the module is installed in the Mainframe, as indicated by the label:

## **Electromagnetic Compatibility**

#### **Radiated Emissions**

To ensure compliance with EN 55011 (1991) a category 5, FTP patch lead, RJ45 cable should be used to connect the LAN port on the processor module marked "10 Base-T".

### **Electrostatic Discharge**

When air discharges, according to IEC801-2 (1991), of up to 8 kV are applied to specific areas of the product occasional errors may be counted.

## **Operators Maintenance**

#### WARNING

NO OPERATOR SERVICEABLE PARTS INSIDE. REFER SERVICING TO QUALIFIED PERSONNEL. TO PREVENT ELECTRICAL SHOCK DO NOT REMOVE COVERS.

### Cleaning

Clean the cabinet using a dry cloth only.

#### **Optical Fibre Cleaning**

It is recommended that the optical connectors be cleaned at regular intervals using the following materials:

| Description         | HP Part<br>Number |

|---------------------|-------------------|

| Blow Brush          | 9300-1131         |

| Isopropyl Alcohol   | 8500-5344         |

| Lens Cleaning Paper | 9300-0761         |

| Adhesive Tape Kit   | 15475-68701       |

#### **CAUTION**

Do not insert any tool or object into the IN or OUT ports of the instrument as damage to or contamination of the optical fibre may result.

- 1. Recall Default settings (STORED SETTINGS 0) and remove the power from the HP 37717C.

- 2. Remove the adapters from the IN and OUT ports.

- 3. Using the blow brush with the brush removed blow through the ferrule of the standard flexible connector and the adapter.

#### **CAUTION**

If the optical fibre of the fixed connector requires further cleaning this entails disassembly of the module which should only be carried out by suitably trained service personnel.

- 4. Apply some isopropyl alcohol to a piece of the cleaning paper and clean the barrel of the adapter. Using a new piece of cleaning paper, clean the face of the adapter. Repeat this operation, using a new piece of cleaning paper each time.

- 5. Lightly press the adhesive side of the tape provided against the front of the adapter, then remove it quickly repeat twice. This removes any particles of cleaning paper which may be present.

- 6. Replace the adapters on the flexible connector.

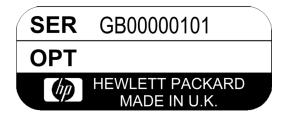

## **Instruments Covered By Manual**

Attached to the rear panel of the instrument is a serial number plate. The serial number plate has a two letter reference denoting country of origin (GB = Great Britain) and an eight digit serial number. The serial number is unique to each instrument and should be quoted in all correspondence with Hewlett-Packard, especially when ordering replacement parts.

Figure 1-2 Serial Number Plate

Table 1-1 Recommended Test Equipment

| Instrument                                                            | Critical Specification                                                            | Recommended Model                         |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------|--|

| Oscilloscope                                                          | 400 MHz Bandwidth, 1 MΩ Input<br>Termination, Telecom mask meas function          | HP 54520A Opt 001 or<br>HP 54810A Opt 001 |  |

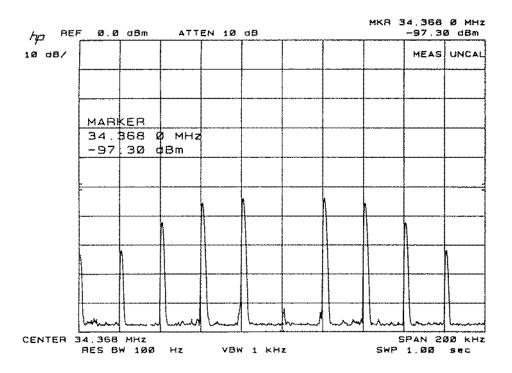

| Spectrum Analyzer                                                     | 200 MHz Bandwidth, 75 $\Omega$ Input, -70 to +20 dBm                              | HP 8568B Opt 001                          |  |

| Frequency Synthesizer                                                 | 75 $\Omega$ Output, Sinewave to 80 MHz, Amplitude to 2.5 V pk-pk, 1 Hz resolution | HP 3335A Opt 001                          |  |

| Frequency Synthesizer                                                 | Sinewave to 2.5 MHz, Amplitude to 5 V pk-pk, 1 Hz Resolution                      | HP 3325B (Qty 2)                          |  |

| Signal Generator                                                      | Sinewave 700 kHz to 170 MHz, Amplitude 500 mV                                     | HP 8657B                                  |  |

| Frequency Counter                                                     | Range 0 to 200 MHz, 2 channels with accuracy <0.1 ppm. (Ratio Mode)               | HP 5335A Opt 010                          |  |

| Optical Power Meter and Sensor<br>Module                              | Range -8 dBm to -15 dBm, Wavelength 1270-1340 nm                                  | HP 8153A and HP 81536A                    |  |

| Power Supply                                                          | Multi-Output System 0-50 V, 0-500 mA, 25 watts o/p                                | HP 6621A                                  |  |

| Lightwave Convertor                                                   | Wavelength 1200 - 1600 nm and Bandwidth<br>from dc. 15 GHz<br>Optical             | HP 11982A                                 |  |

| Optical Attenuator                                                    | Wavelength 1200 - 1600 nm, Range 0 - 30 dB                                        | HP 8157A                                  |  |

| FC/PC Optical Interface<br>Connector                                  | Unique                                                                            | HP 81000FI                                |  |

| Optical Cables                                                        | Unique                                                                            | HP 11871A (Qty 2)                         |  |

| PDH Structured Test Set<br>or Digital Transmission Frame<br>Generator | Unique                                                                            | HP 37717C Opt UKJ or<br>HP 37729A         |  |

| Jitter Measurement Module                                             | Unique                                                                            | HP 37717C Opt UHN or any<br>Jitter Rx     |  |

| Attenuator                                                            | 6 dB, $50\Omega$ , 0 to 200 MHz                                                   | HP 8491A Opt 006                          |  |

| Attenuator                                                            | $3~\mathrm{dB}, 50\Omega$ , $0~\mathrm{to}~200~\mathrm{MHz}$                      | HP 8491A Opt 003                          |  |

| Cable Simulator #1                                                    | $80~\mathrm{metres}$ of $75\Omega$ coaxial cable                                  | 8120-0049 (80 m)                          |  |

| Cable Simulator #2                                                    | $60~{ m metres}~{ m of}~75 \Omega~{ m coaxial}~{ m cable}$                        | 8120-0049 (60 m)                          |  |

| Cable Simulator #3                                                    | $70~{ m metres}~{ m of}~75\Omega~{ m coaxial}~{ m cable}$                         | 8120-0049 (70 m)                          |  |

| Cable Simulator #4                                                    | $30~{ m metres}~{ m of}~75\Omega$ coaxial cable                                   | 8120-0049 (30 m)                          |  |

| Converter                                                             | $75 \Omega$ Unbalanced to $120 \Omega$ Balanced                                   | HP 15508C                                 |  |

Table 1-1 Recommended Test Equipment, continued

| Instrument                           | Critical Specification   | Recommended Model   |

|--------------------------------------|--------------------------|---------------------|

| ECL Termination                      | Unique                   | HP 10086A           |

| Blocking Capacitor                   | 0.18 μf                  | HP 10240A           |

| Cable Attenuator                     | Unique                   | HP 8120-0039 (70 m) |

| $75 \Omega / 50 \Omega$ Matching Pad | Insertion Loss 5.7 dB    | HP 11852B (Qty 2)   |

| $75 \Omega$ Termination              | 0 to 200 MHz             | HP 15522-80010      |

| T Connector                          | BNC to Dual BNC          | HP 1250-0781        |

| Adaptor                              | N Type (f) to BNC (m)    | 1250-1534 (Qty 2)   |

| Adaptor                              | N Type (m) to N Type (m) | 1250-1475 (Qty 2)   |

| Adaptor                              | SMA to BNC               | 1250-1787 (Qty 2)   |

| RS-232-C Loopback                    | Unique                   | 5060-4462           |

| Oscilloscope Pod                     | 10 <b>k</b> Ω            | HP 54001A           |

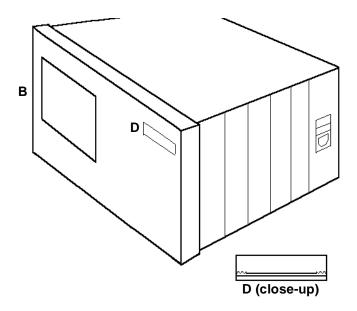

## Installation

This section contains information and instructions required to prepare the HP 37717C Communications Performance Analyzer for use. Included in this section are the initial inspection procedures, power and grounding requirements, fuse selection procedure, installation information, operators maintenance and instructions on repackaging for shipment.

**Initial Inspection**

Preparation for Use

**Operators Maintenance**

**Hewlett-Packard Interface Bus**

**Operating Environment**

Storage and Shipment

## **Initial Inspection**

#### WARNING

TO AVOID HAZARDOUS ELECTRICAL SHOCK, DO NOT PERFORM ELECTRICAL TESTS WHEN THERE ARE SIGNS OF SHIPPING DAMAGE TO ANY PORTION OF THE OUTER ENCLOSURE (COVERS, PANELS, METERS).

Inspect the shipping container for damage. If the shipping container or cushioning material is damaged, it should be kept until the contents of the shipment have been checked for completeness and the instrument has been checked both mechanically and electrically. Procedures for checking electrical operation are given in The Calibration Manual. If the contents of the shipment are incomplete, if there is mechanical damage or defect, notify the nearest Hewlett-Packard Office. If the instrument does not pass the electrical performance tests given in the Calibration Manual, notify the nearest Hewlett-Packard office. If the shipping container is also damaged, or the cushioning material shows signs of stress, notify the carrier as well as the nearest Hewlett-Packard office. Keep the shipping materials for the carrier's inspection. The Hewlett-Packard office will arrange for repair or replacement without waiting for claim settlement.

Installation Preparation for Use

## **Preparation for Use**

#### WARNING

IF THIS INSTRUMENT IS NOT USED AS SPECIFIED, THE PROTECTION PROVIDED BY THE EQUIPMENT COULD BE IMPAIRED. THIS INSTRUMENT MUST BE USED IN A NORMAL CONDITION (IN WHICH ALL MEANS OF PROTECTION ARE INTACT) ONLY.

#### WARNING

FOR CONTINUED PROTECTION AGAINST FIRE HAZARD REPLACE FUSE ONLY WITH SAME TYPE AND RATINGS (SEE TABLE 2-1).

#### **Power Requirements**

The HP 37717C Communications Performance Analyzer requires a power source of 90 V to 132 V ac and 198 V to 264 V ac at a frequency between 47 Hz and 63 Hz (nominal).

Total power consumption is 450 VA (maximum).

The fuse rating for the power source is given in Table.

Table 2-1 Fuses

| Line Voltage | Fuse Rating    | HP Part Number |

|--------------|----------------|----------------|

| 90V to 264V  | 5A Timed, 250V | 2110-1120      |

#### **Power Cord**

The power cord supplied with each instrument varies with the country of destination. Figure 2-1 illustrates the standard power plug and cord configurations that are commonly used. The part number shown beneath each plug is the part number of the appropriate power cord and plug. If the appropriate power cord is not included with the instrument notify the nearest Hewlett-Packard office and a replacement will be provided.

#### WARNING

TO AVOID THE POSSIBILITY OF INJURY OR DEATH, THE FOLLOWING PRECAUTIONS MUST BE FOLLOWED BEFORE THE INSTRUMENT IS SWITCHED ON:

- (a) Note that the protection provided by grounding the instrument cabinet may be lost if any power cable other than the three-pronged type is used to couple the ac line voltage to the instrument.

- (b) If this instrument is to be energized via an auto-transformer to reduce or increase the line voltage, make sure that the common terminal is connected to the neutral pole of the power source.

- (c) The power cable plug shall only be inserted into a socket outlet provided with a protective ground contact. The protective action must not be negated by the use of an extension cord without a protective conductor (grounding).

**Operators Maintenance**

Figure 2-1 Power Cord Part Numbers

## **Operators Maintenance**

### Fuse Replacement

Only the ac line fuse located at the side of the instrument may be replaced by the operator.

#### WARNING

ALL OTHER FUSE REPLACEMENT SHOULD ONLY BE CARRIED OUT BY SUITABLY TRAINED SERVICE PERSONNEL AWARE OF THE HAZARDS INVOLVED.

BEFORE REMOVING THE FUSE, THE AC LINE POWER CORD SHOULD BE DISCONNECTED FROM THE POWER SOURCE AND THE OTHER END DISCONNECTED FROM THE INSTRUMENT.

ONLY USE A FUSE OF THE CORRECT RATING AS LISTED IN TABLE 2-1.

Use a small flat bladed tool to remove the fuse holder from the Power Supply Line Filter Assembly (located between the Power ON /OFF switch and the Power Input connector. The cap and the fuse can then be removed and the fuse changed for another of the correct rating. The fuse rating and HP part number are listed in Table 2-1.

#### **Line Voltage Selector Switch**

The Line Voltage Selector switch has 2 positions:

100 - 120 V

200 - 240 V

### CAUTION

Before switching on this instrument, make sure that the line voltage selector switch is set to the voltage of the power supply. Ensure the supply voltage is in the specified range.

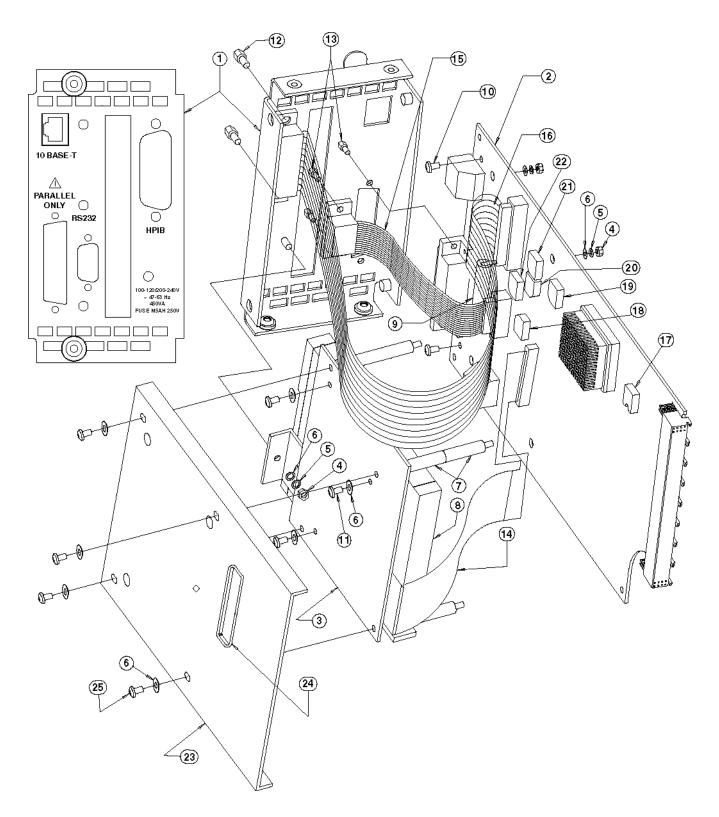

### **Hewlett-Packard Interface Bus**

The HP 37717C (Option A3B or A3D) is connected to the HP-IB by means of an appropriate HP-IB cable. The HP-IB interconnecting cables available are listed in Table 2-2.

| Table 2-2 HP-IB In | 2 HP-IB Interconnecting Cables |  |  |

|--------------------|--------------------------------|--|--|

| Length             | Accessory Number               |  |  |

| Length    | Accessory Number |

|-----------|------------------|

| 1 meter   | HP 10833A        |

| 2 meters  | HP 10833B        |

| 4 meters  | HP 10833C        |

| 0.5 meter | HP 10833D        |

To achieve interface design performance standards, restrictions are placed on the HP-IB system cable lengths. These restrictions allow the bus interface electronics to maintain correct line voltage levels and timing relationships.

When connecting an HP-IB system the following rules should be observed:

The total HP-IB cable length used must be less than or equal to 20 meters (65.6 feet).

The total HP-IB cable length used must be less than or equal to 2 meters (6 feet) × the total number of devices connected to the bus.

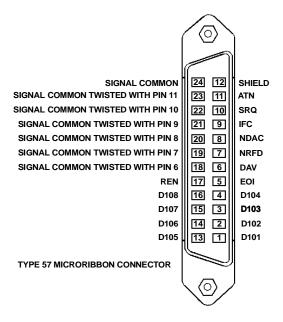

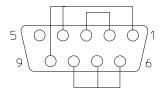

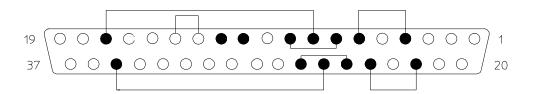

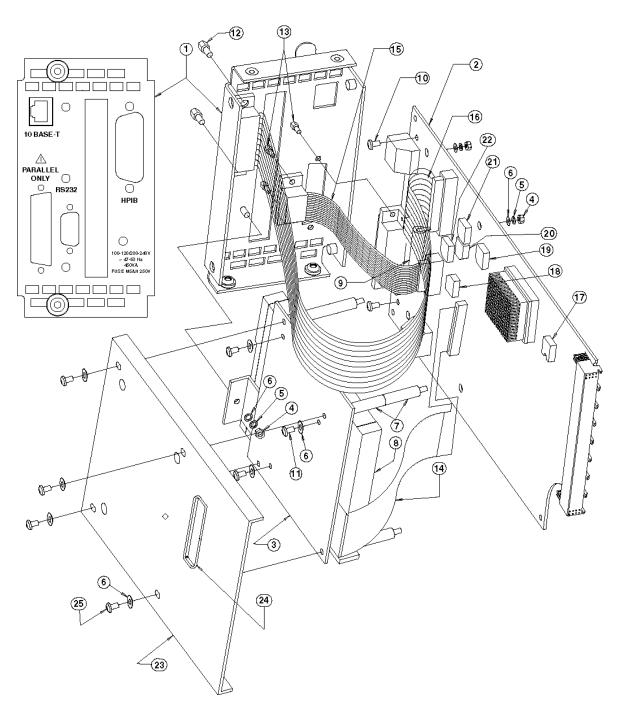

A standard HP-IB connector is provided on the instrument CPU front panel. The connections and HP-IB logic levels are shown in Figure 2-2. The mating connector part number is HP 1251-0293 or Amphenol 57-30240.

Figure 2-2 HP-IB Connections and Logic Levels

### **HP-IB Address Selection**

The HP 37717C (Option A3B or A3D) HP-IB address is accessed on the OTHER display under the COMMS CONTROL function.

The address can be set to any value between 0 and 30 inclusive using [4] [1] and the display softkeys.

## **Operating Environment**

The instrument may be operated in temperatures within the range 0 degrees to +45 degrees centigrade at altitudes up to 3,050 meters (10,000 feet). At all times the instrument should be protected from temperature extremes and environments which could cause condensation within the instrument.

#### CAUTION

VENTILATION REQUIREMENTS: When installing the instrument in a cabinet, the convection into and out of the instrument must not be restricted. The ambient temperature (outside the cabinet) must be less than the maximum operating temperature of the instrument by  $4^{0}\mathrm{C}$  for every 100 watts dissipated in the cabinet. If the total power dissipated in the cabinet is greater than 800 watts, then forced convection must be used.

## Storage and Shipment

The instrument may be stored or shipped in environments within the following limits:

**Temperature.**  $-40^{\circ}$  C to  $+65^{\circ}$  C

**Altitude.** Up to 15,200 meters (50,000 feet)

The instrument should also be protected from temperature extremes which could cause condensation within the instrument.

### Repackaging for Shipment

**Tagging for Service**. If the instrument is being returned to Hewlett- Packard for service, please complete a repair tag and attach it to the instrument.

**Original Packaging**. Containers and materials identical to those used in factory packaging are available from Hewlett-Packard offices. If the instrument is being returned to Hewlett-Packard for servicing, attach a tag indicating the type of service required, return address, model number, and full serial number. Mark the container FRAGILE to ensure careful handling. In any correspondence, refer to the instrument by model number and full serial number.

**Other Packaging**. The following general instructions should be followed when repackaging with commercially available materials:

Wrap instrument in heavy paper or plastic. If the instrument is being shipped to Hewlett-Packard, attach a tag indicating the type of service required, return address, model number and full serial number.

Use a strong shipping container. A double wall carton made of 350 pound test material is adequate.

Use a layer of shock absorbing material 70 to 100 mm (3 to 4 inch) thick, around all sides of the instrument to provide firm cushioning and prevent movement inside the container. Protect the Front Panel controls and Rear Panel connectors with cardboard.

Seal shipping container securely.

Mark shipping container FRAGILE to ensure careful handling.

In any correspondence, refer to instrument by model number and full serial number.

# **Adjustments**

#### Introduction

This section contains the adjustment procedures required for the HP 37717C. These procedures will allow the instruments to be adjusted to meet the published specifications.

## Safety Considerations

The HP 37717C is a Safety Class 1 (IEC) instruments. (This means that the instruments are provided with protective earth terminals.) This section contains warnings and cautions which must be followed for your protection and safety and to avoid damage to the instruments.

#### WARNING

MAINTENANCE DESCRIBED HEREIN IS PERFORMED WITH POWER SUPPLIED TO THE INSTRUMENT AND PROTECTIVE COVERS REMOVED. SUCH MAINTENANCE SHOULD ONLY BE PERFORMED BY SERVICE TRAINED PERSONNEL WHO ARE AWARE OF THE HAZARDS INVOLVED (e.g. FIRE AND ELECTRICAL SHOCK). WHERE MAINTENANCE CAN BE PERFORMED WITHOUT POWER APPLIED, THE POWER SHOULD BE REMOVED.

## Requirements for Adjustments

Before carrying out any adjustments, check the Time and Date logged for each of the Calibration item adjustments as follows:

- 1 Switch on the instrument then press the **OTHER** key.

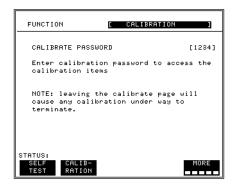

- **2** Press the MORE softkey select the **CALIBRATION** function.

- 3 Select Calibration password and set to [1243] using the INCREASE DIGIT and DECREASE DIGIT softkeys.

- 4 Select each Calibration item in turn and note the Time and Date of the last valid Calibration. If any of these are invalid or greater than 1 year, it is recommended that the soft adjustments associated with that item are carried out.

It is also recommended that adjustments be performed if a failure occurs in one or more of the Performance Tests. Performance Tests are provided in the HP 37717C Calibration manual. The Performance Test failure will usually indicate which parameter needs to be adjusted, but if in doubt, or if the adjustment does not bring the parameter within specification, refer to the Service Section in this Manual.

Adjustments Adjustment Type

## **Adjustment Type**

The HP 37717C contain two types of adjustments.

**Hard Adjustment** - this is done using an analog on-board component such as a variable resistor or capacitor.

**Soft Adjustment** - this may be automatic or semi-automatic. When the adjustment is completed calibration data is stored in a special Ram on the module or the CPU. The instrument will also log the Time and Date of the adjustment in the Calibration Menu.

### List of Soft Adjustments

The following table provides a list of all "Soft" adjustments (stored in the memory) in the HP 37717C.

| Adjustment Title                 | Page No | Where Required |

|----------------------------------|---------|----------------|

| 10 MHz Reference Clock Frequency | 3-8     | All Units      |

#### NOTE

The Internal Clock Time and Date must be set up before carrying out any "soft" adjustment (Refer to Operating Manual).

## List of Adjustable Components

The following table provides a list of all adjustable components (hard adjustments) within the HP 37717C.

Table 3-1 Adjustable Components

| Adjustable Component | Page No                       | Adjustment Title                                          |  |

|----------------------|-------------------------------|-----------------------------------------------------------|--|

| A4R25                | 3-8                           | 10 MHz Reference Clock Frequency & VCXO<br>CAL Disk-Drive |  |

|                      | UPDH Transmitter (Option UKK) |                                                           |  |

| A7R1                 | 3-10                          | CMI Tx Pulse Amplitude                                    |  |

| A7R2                 | 3-10                          | CMI Tx Eye-Diagram Symmetry                               |  |

| A7R3                 | 3-10                          | CMI Pulse Mark : Space Ratio                              |  |

| A7R4                 | 3-10                          | Ternary Pulse Amplitude (positive)                        |  |

| A7R5                 | 3-10                          | Ternary Pulse Amplitude (negative)                        |  |

|                      | UPDH Receiver (Option UKK)    |                                                           |  |

| A6R1                 | 3-13                          | PDH 704 kHz Rx Recovered Clock                            |  |

| A6R2                 | 3-13                          | PDH 2048 kHz Rx Recovered Clock                           |  |

| A6R3                 | 3-13                          | PDH 8448 kHz Rx Recovered Clock                           |  |

Adjustments Adjustment Type

Table 3-1 Adjustable Components, continued

| Adjustable Component                                     | Page No                         | Adjustment Title                       |  |

|----------------------------------------------------------|---------------------------------|----------------------------------------|--|

| A6R4                                                     | 3-13                            | PDH 34368 kHz Rx Recovered Clock       |  |

| A6C154                                                   | 3-13                            | PDH 139264 kHz Rx Recovered Clock      |  |

|                                                          | SDH Trans                       | mitter (Option A1T)                    |  |

| A9R53                                                    | 3-17                            | STM-1 All Zeros Pulse Mark:Space Ratio |  |

| A9R38                                                    | 3-17                            | STM-1 All Ones Pulse Mark:Space Ratio  |  |

| A9R22                                                    | 3-17                            | STM-1 Tx Pulse Amplitude               |  |

|                                                          | SDH Rece                        | eiver (Option A1T)                     |  |

| A9C230                                                   | 3-20                            | STM-1 Rx CMI Clock Recovery            |  |

|                                                          | SDH Standar                     | d Clock (Options A1T)                  |  |

| A8C104                                                   | 3-22                            | SDH Rx Offset Clock Recovery           |  |

| ST                                                       | M-1 Optical T                   | ransmitter (Option UH1)                |  |

| A11R1                                                    | 3-25                            | STM-1 Optics Modulation Depth          |  |

| 1310 nm STM1/4 Optical Transmitter (Options USN and UKT) |                                 |                                        |  |

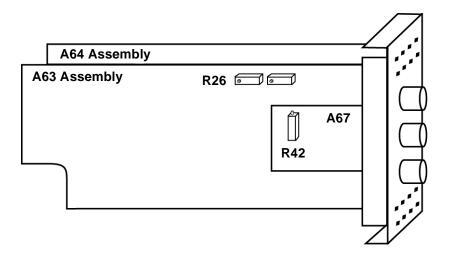

| A63R26                                                   | 3-27                            | STM4 Optical Power Level               |  |

| 158                                                      | 50 nm STM1/4                    | Optical Transmitter USN                |  |

| A67R42                                                   | 3-29                            | STM4 Optical Power Level               |  |

|                                                          | Jitter Transmitter (Option UHK) |                                        |  |

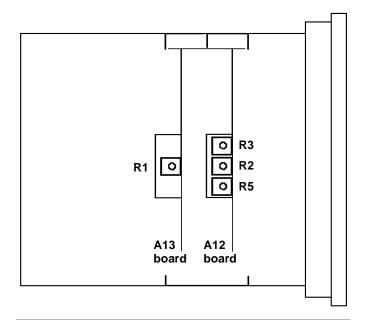

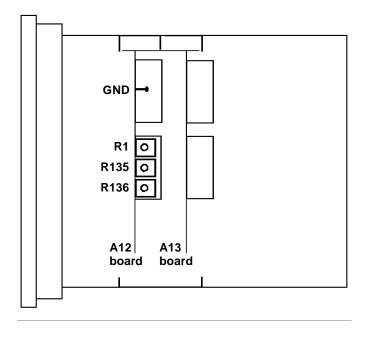

| A12R136                                                  | 3-31                            | 34 MHz Duty Cycle                      |  |

| A12R135                                                  | 3-31                            | 140 MHz Duty Cycle                     |  |

| A12R2                                                    | 3-31                            | DC Offset                              |  |

| A12R5                                                    | 3-31                            | Residual Amplitude                     |  |

| A12R1                                                    | 3-31                            | Control Loop Gain                      |  |

|                                                          | Jitter Genera                   | tor (Options A3K, 140)                 |  |

| R69                                                      | 3-40                            | 2 MHz VCO Duty Cycle                   |  |

| R47                                                      | 3-40                            | 8 MHz VCO Duty Cycle                   |  |

| R40                                                      | 3-40                            | 34 MHz VCO Duty Cycle                  |  |

| R56                                                      | 3-40                            | 140 MHz VCO Duty Cycle                 |  |

| R53                                                      | 3-40                            | Control Loop DC Offset                 |  |

| R39                                                      | 3-40                            | Control Loop DC Offset                 |  |

| R21                                                      | 3-40                            | Loop Gain                              |  |

| L2                                                       | 3-40                            | 2 MHz Ref Input Min. Jitter            |  |

|                                                          | l .                             | ı                                      |  |

Adjustment Type

Table 3-1 Adjustable Components, continued

| Adjustable Component          | Page No                          | Adjustment Title                      |  |

|-------------------------------|----------------------------------|---------------------------------------|--|

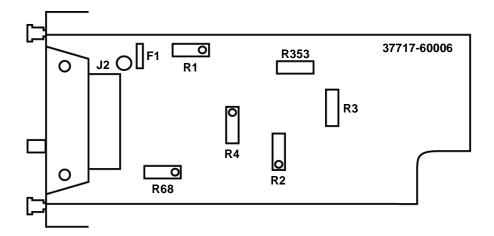

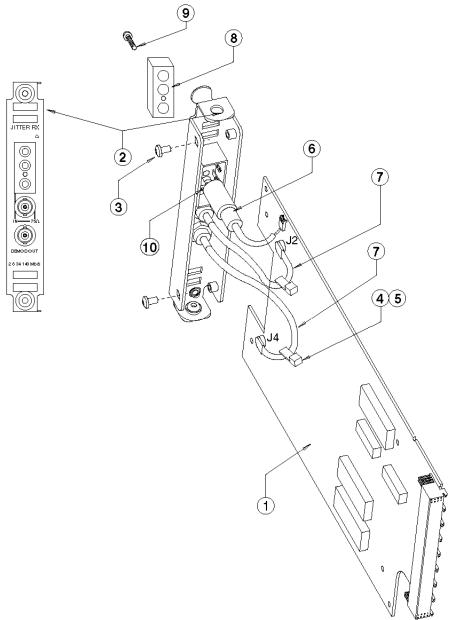

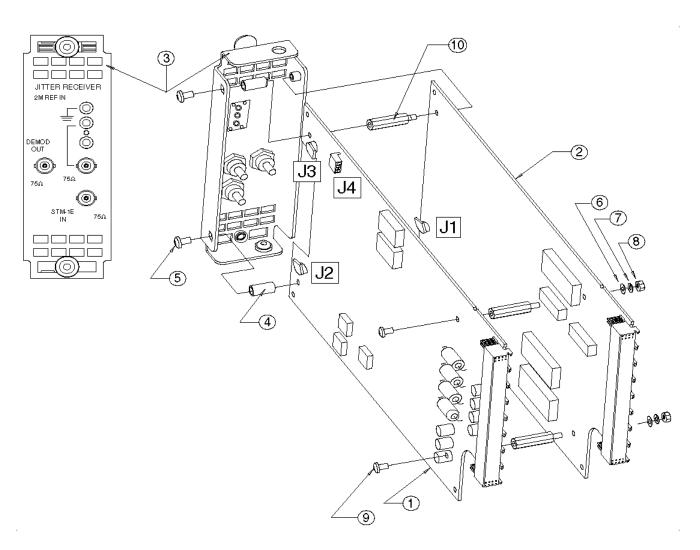

| Jitter Receiver (Option UHN)  |                                  |                                       |  |

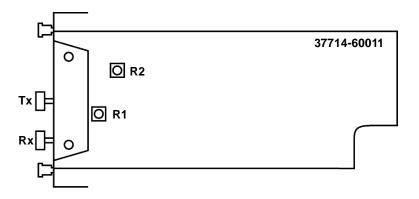

| R2, R4                        | 3-44                             | Measurement Loop Offset               |  |

| R1                            | 3-44                             | Jitter Hits Threshold Level           |  |

| R68                           | 3-44                             | Demod Jitter Output Amplitude         |  |

| L21                           | 3-44                             | Wander Reference Recovered Clock      |  |

|                               | Jitter Receive                   | er (Options A3L, A3M)                 |  |

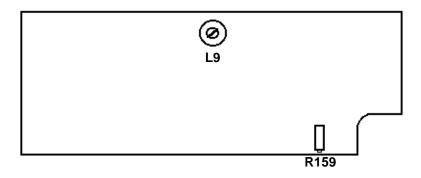

| A18R159                       | 3-50                             | Recovered Clock                       |  |

| A18L9                         | 3-50                             | Wander Reference Recovered Clock      |  |

| Jit                           | ter Receiver (                   | (Options A1M, A1N, A1P)               |  |

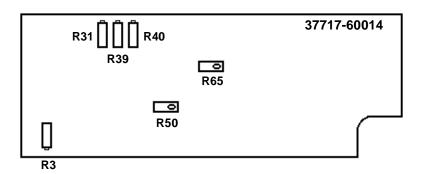

| R40                           | 3-54                             | False Lock Set                        |  |

| R31                           | 3-54                             | Jitter Hits Level                     |  |

| R3                            | 3-54                             | Demod. Jitter Output                  |  |

| Jitter Receive                | r Setup (Opti                    | ons A3L, A3M, A3N, A3P, A3V, A3W)     |  |

| R157                          | 3-61                             | Meas Loop Offset                      |  |

| R120                          | 3-61                             | Meas Loop Offset                      |  |

| R73                           | 3-61                             | Narrowband Det. Leakage               |  |

| R54                           | 3-61                             | Narrowband Det. Leakage               |  |

| R2                            | 3-61                             | Demod Jitter Output                   |  |

| R79                           | 3-61                             | Main Lock Detect                      |  |

| SPI                           | OH Transmitte                    | er (Options UKJ and USA)              |  |

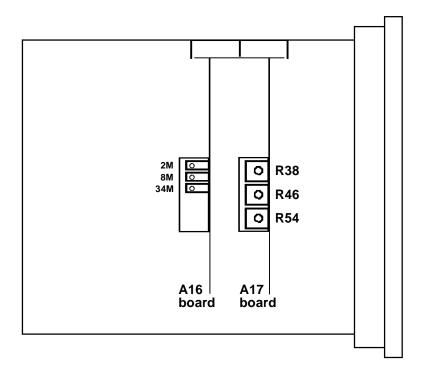

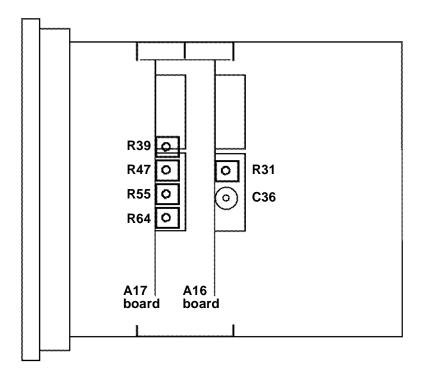

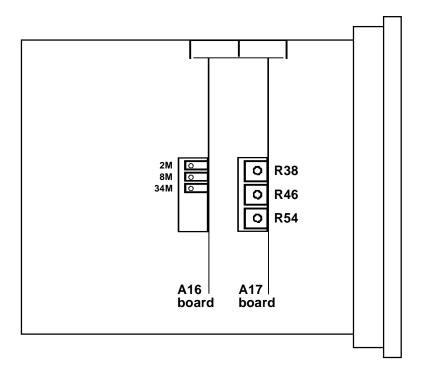

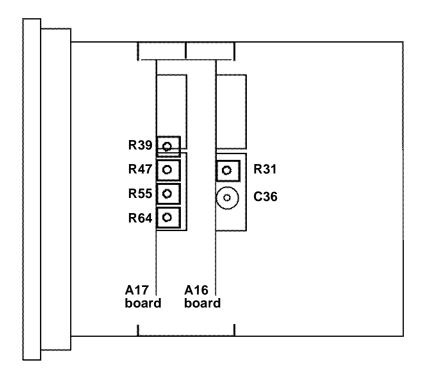

| A17R39                        | 3-67                             | CMI Tx Pulse Amplitude                |  |

| A17R47,55                     | 3-67                             | CMI Tx Mark Space Ratio               |  |

| A17R46                        | 3-67                             | Ternary Pulse Amplitude (positive)    |  |

| A17R54                        | 3-67                             | Ternary Pulse Amplitude (negative)    |  |

|                               | SPDH Receiver (Options UKJ, USA) |                                       |  |

| A16R30                        | 3-71                             | 2048 kHz Recovered Clock frequency    |  |

| A16R38                        | 3-71                             | 8448 kHz Recovered Clock frequency    |  |

| A16R46                        | 3-71                             | 34368 kHz Recovered Clock frequency   |  |

| A16C154                       | 3-71                             | 139,264 kHz Recovered clock frequency |  |

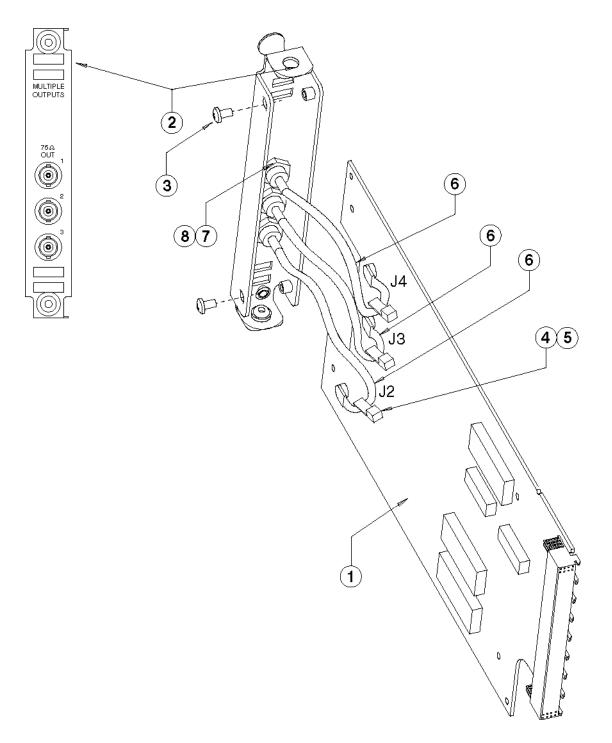

| Multiple Outputs (Option UHC) |                                  |                                       |  |

Adjustments Warm-Up Time

Table 3-1 Adjustable Components, continued

| Page No                              | Adjustment Title                                                                                                        |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| 3-74                                 | VCO Duty Cycle (Unstructured PDH Module fitted)                                                                         |  |

| 3-74                                 | VCO Duty Cycle (Structured PDH Module fitted)                                                                           |  |

| 3-74                                 | CMI Tx Pulse Amplitude (Output 2)                                                                                       |  |

| 3-74                                 | CMI Tx Pulse Amplitude (Output 3)                                                                                       |  |

| 3-74                                 | CMI Tx Pulse Amplitude (Output 4)                                                                                       |  |

| M Cell Layer                         | Transmitter (Option UKZ)                                                                                                |  |

| 3-77                                 | Term Pulse Amplitude +ve                                                                                                |  |

| 3-77                                 | Term Pulse Amplitude -ve                                                                                                |  |

| ATM Cell Layer Receiver (Option UKZ) |                                                                                                                         |  |

| 3-83                                 | 1.544 MHz Recovered Clock                                                                                               |  |

| 3-83                                 | 2 MHz Recovered Clock                                                                                                   |  |

| 3-83                                 | 34 MHz Recovered Clock                                                                                                  |  |

| 3-83                                 | 44 MHz Recovered Clock                                                                                                  |  |

| Binary Int                           | erface (Option UH3)                                                                                                     |  |

| 3-88                                 | -5.2 V Supply                                                                                                           |  |

| STM Clock Setup (Option A3R)         |                                                                                                                         |  |

| 3-94                                 | Transmitter Minimum Jitter                                                                                              |  |

| 3-94                                 | Receiver Minimum Jitter                                                                                                 |  |

| SDH Se                               | tup (Option A3R)                                                                                                        |  |

| 3-101                                | Mark/Space Adjust                                                                                                       |  |

|                                      | 3-74 3-74 3-74 3-74 3-74 3-74 M Cell Layer 3-77 TM Cell Laye 3-83 3-83 3-83 Binary Inte 3-88 STM Clock 3-94 3-94 SDH Se |  |

# Warm-Up Time

To ensure adjustment accuracy, the equipment must be switched on for a minimum of 30 minutes before carrying out any adjustment.

## **Adjustment Sequence**

The adjustments should be performed in the sequence given in Table above. The 10 MHz Reference Clock frequency adjustment and VCXO Calibration must always be performed first.

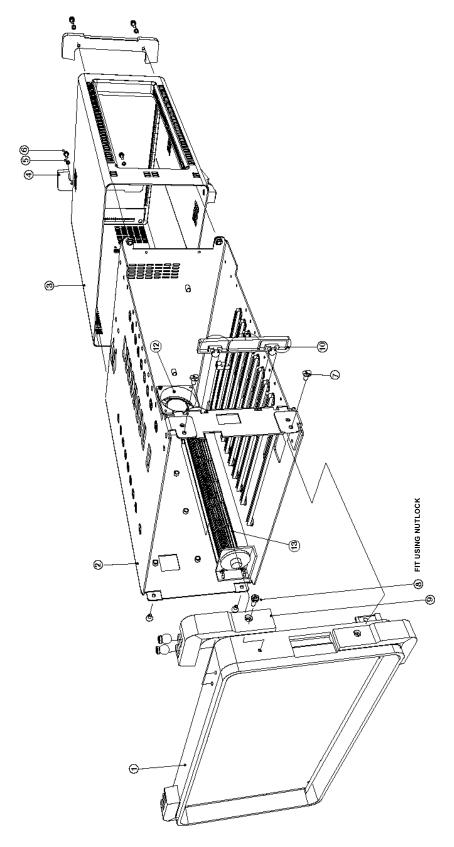

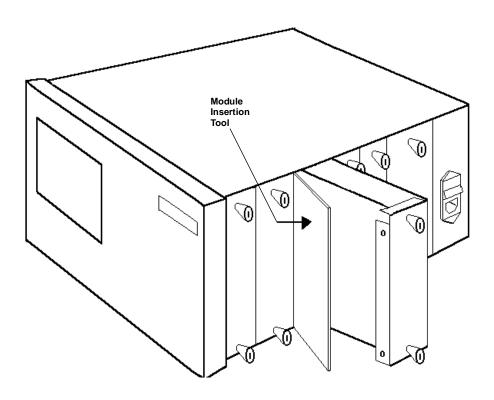

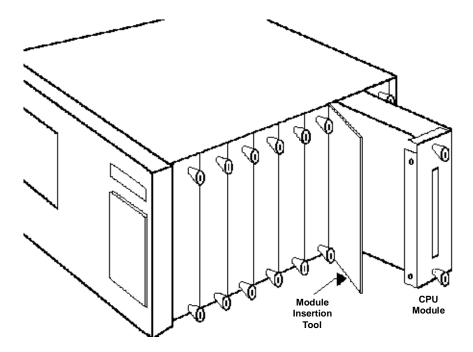

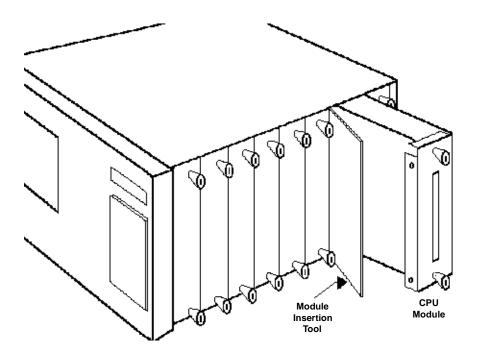

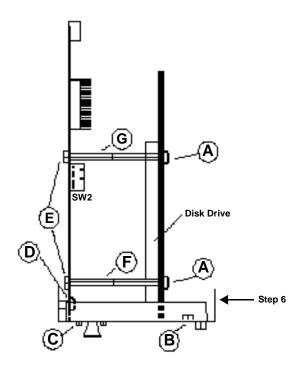

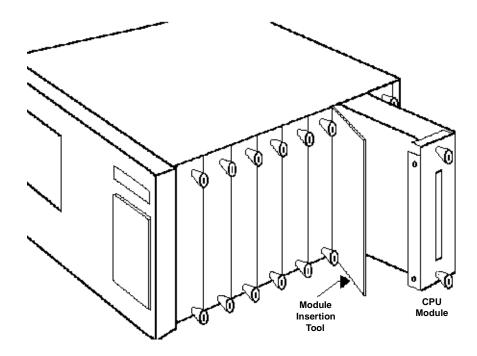

## Access to Adjustable Components

To gain access to adjustable components, proceed as follows;

- 1 Switch off the instrument and disconnect the power cord and any interconnecting cables.

- 2 Place the instrument face down on the workbench.

- 3 Remove the 4 screws securing the rubber feet to the rear panel.

- **4** If Optical Modules are fitted unscrew the optical shield from the input and output connectors.

- **5** Withdraw the outer cabinet sleeve back, and out of the instrument.

Most adjustable components may now be accessed through the slots in the top or bottom of the instrument chassis. Where an Extender Card is required, this will be covered in the particular adjustment procedure. When all adjustments have been completed, re-assemble the instrument as a reversal of the above procedure.

## **Equipment Required**

Equipment required to perform these adjustments is listed on page 1-9. Equipment required to make an individual adjustment is listed in the particular adjustment procedure. Any equipment which meets or exceeds the listed critical specification may be substituted.

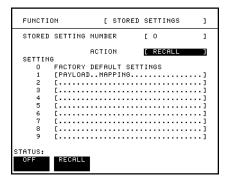

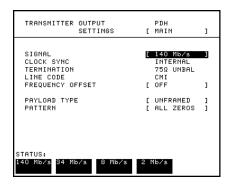

## **Recall Default Settings**

Some adjustments require the HP 37717C to be set to a pre-defined (default) state at the beginning of each test. The pre-defined default settings are listed in Appendix A.

1 Press OTHER; then use the and less to select and set up the STORED SETTINGS as shown below.

**2** Press **RECALL** to recall the instrument default settings.

The instrument display will blank for a few seconds while the settings are recalled and the status display will indicate stored settings number 0 recalled.

## 10 MHz Reference Clock Frequency and VCXO

### Adjustment Reference

10 MHz Reference Clock Source

A4R25

### **Description**

The 10 MHz Reference Clock Source is calibrated by connecting to a Frequency Counter and adjusting within limits.

The VCXO's are calibrated by running the instrument automatic calibration items.

### **Equipment Required**

Frequency Counter HP 5335A Opt 001

10:1 Oscilloscope Probe HP 10435A

### **Procedure**

#### 10 MHz Reference Clock Frequency

- 1 Recall the HP 37717C Default settings with the following key sequence:

OTHER, then select STORED SETTINGS , set STORED SETTING NUMBER to 0 and ACTION to RECALL.

- **2** Select the **CALIBRATION** function on the **OTHER** display.

- 3 Using [], DECREASE DIGIT and [], INCREASE DIGIT set the CALIBRATE PASSWORD to [1243].

- 4 Select CALIBRATION ITEM to 10 MHz REF and MODE to MANUAL.

- **5** Select Frequency A and 1 M $\Omega$  input impedance on the Frequency Counter.

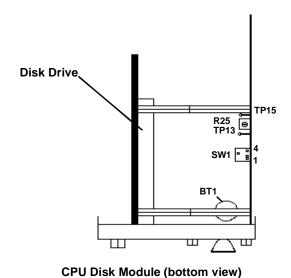

- 6 Connect the Frequency Counter Input A, via the Oscilloscope probe, to TP15 on the A4 Processor Assembly. Ground the probe on TP13 (ground) on this assembly. These Test Points are accessible through a slot in the bottom of the instrument.

- 7 Adjust A4R25 to obtain a Counter reading of 10,000,000 Hz.

- 8 Select the MEASURED FREQUENCY field on the HP 37717C display and enter the counter frequency reading using []-, DECREASE DIGIT and []-, INCREASE DIGIT keys.

- **9** You must change the displayed frequency or the new Calibration Time and Date will not be entered in memory. The Time and Date must be correctly set up see Operating Manual.

## VCXO Calibration (PDH Options)

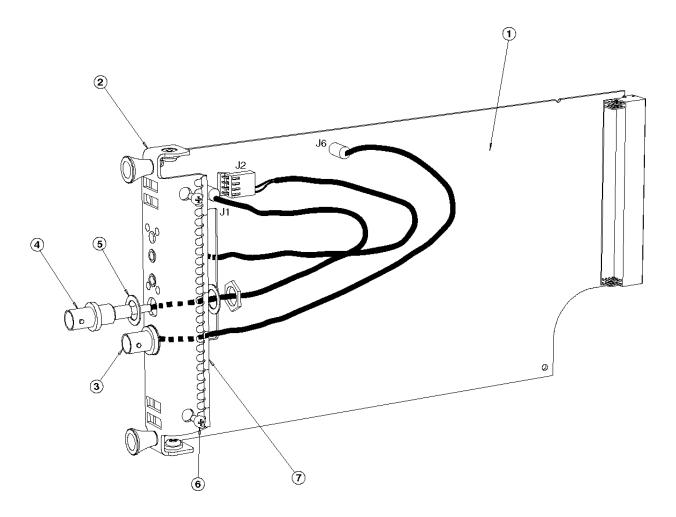

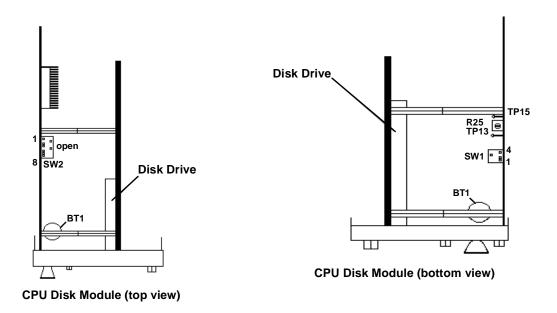

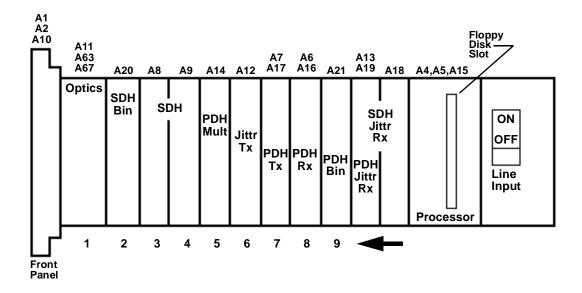

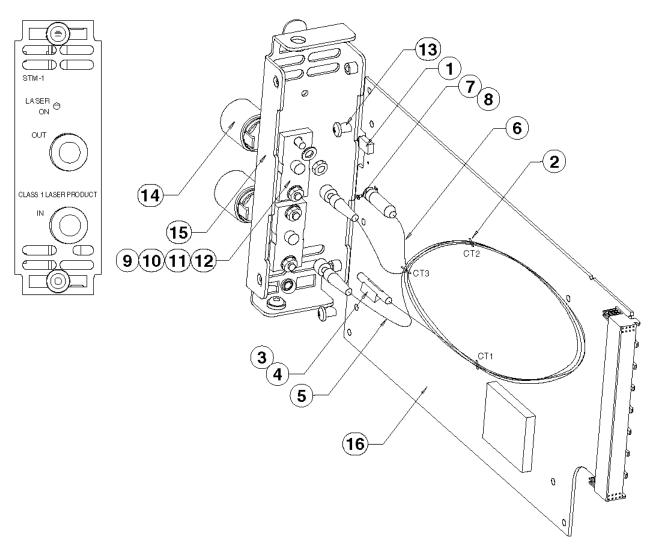

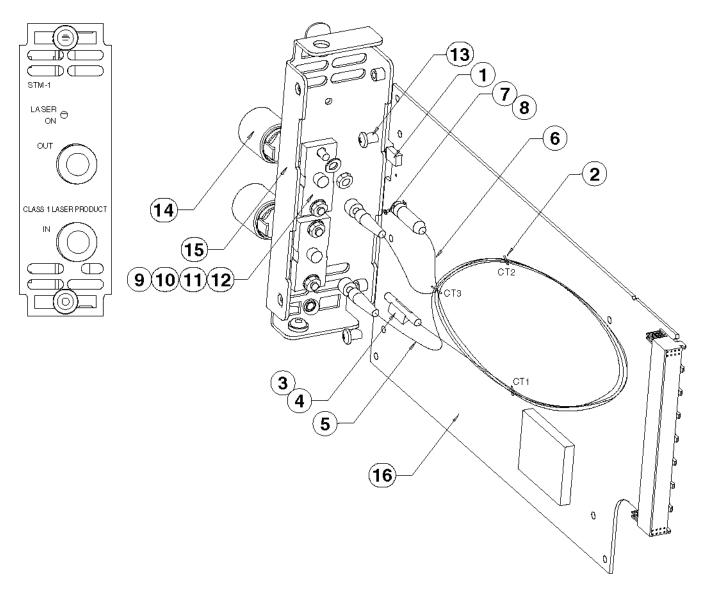

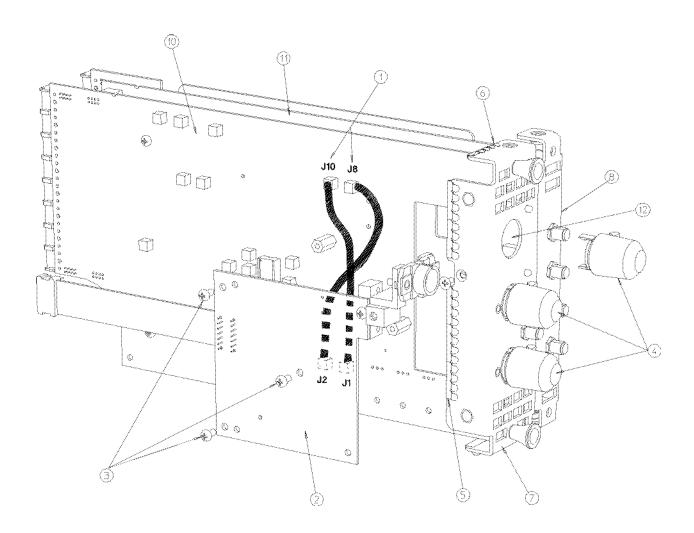

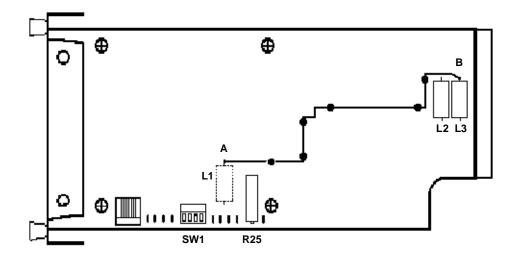

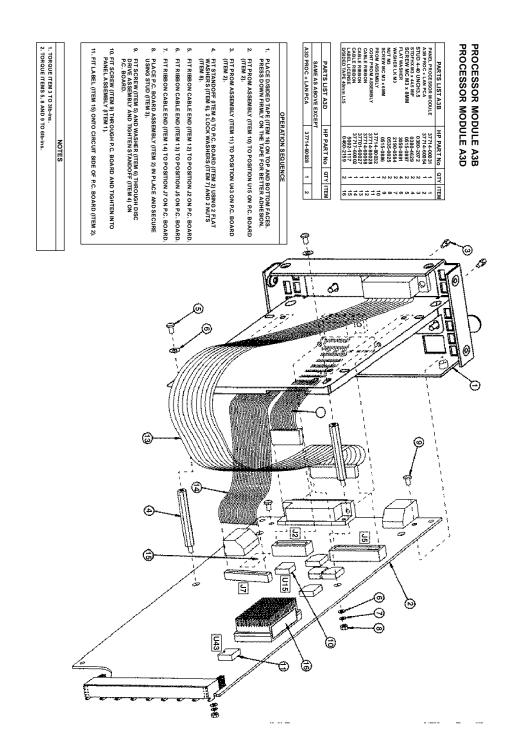

Figure 3-1 Processor Module (underside) Adjustable Components

- **10** Set the CALIBRATION to VCXOs and press [RUN/STOP] to start the calibration routine.

- 11 When Calibration is finished, the Calibration Time and Date will appear next to each VCXO on the display.

- **12** Disconnect all test equipment.

# **Unstructured PDH Transmitter (Option UKK)**

A7 PDH Transmitter Assembly.

## Adjustment Reference

| CMI Tx Pulse Amplitude             | A7R1 |

|------------------------------------|------|

| CMI Tx Eye-diagram Symmetry        | A7R2 |

| CMI Tx Mark:Space Ratio            | A7R3 |

| Ternary Pulse Amplitude (positive) | A7R4 |

| Ternary Pulse Amplitude (negative) | A7R5 |

## Description

An Oscilloscope is connected to the Data Output port and A7R1, R2 and R3 are adjusted to optimize the displayed CMI pulse Amplitude, Mark to Space Ratio and Eye-Diagram. The positive and negative ternary pulse amplitudes are also set using R4 and R5 on this assembly.

## **Equipment Required**

| Oscilloscope                 | HP 54520A |

|------------------------------|-----------|

| $75/\!50\Omega$ Matching Pad | HP 11852B |

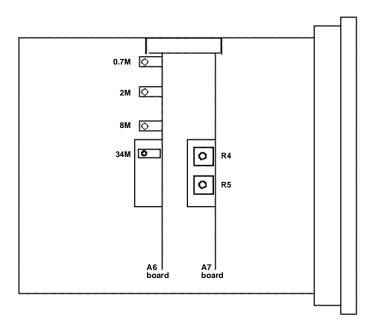

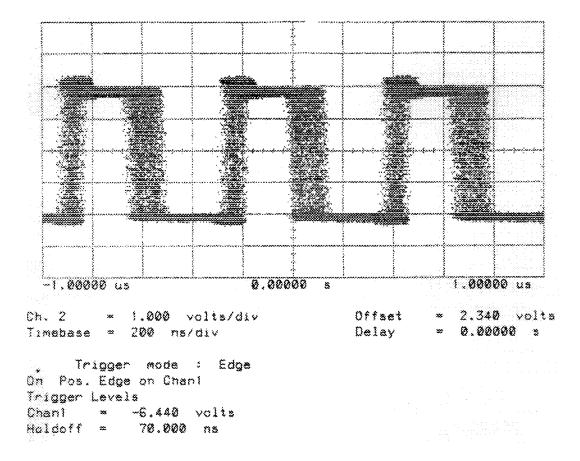

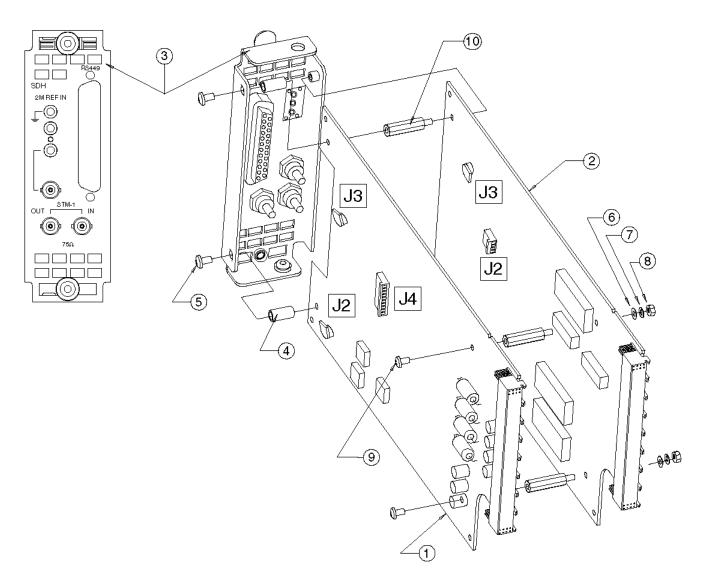

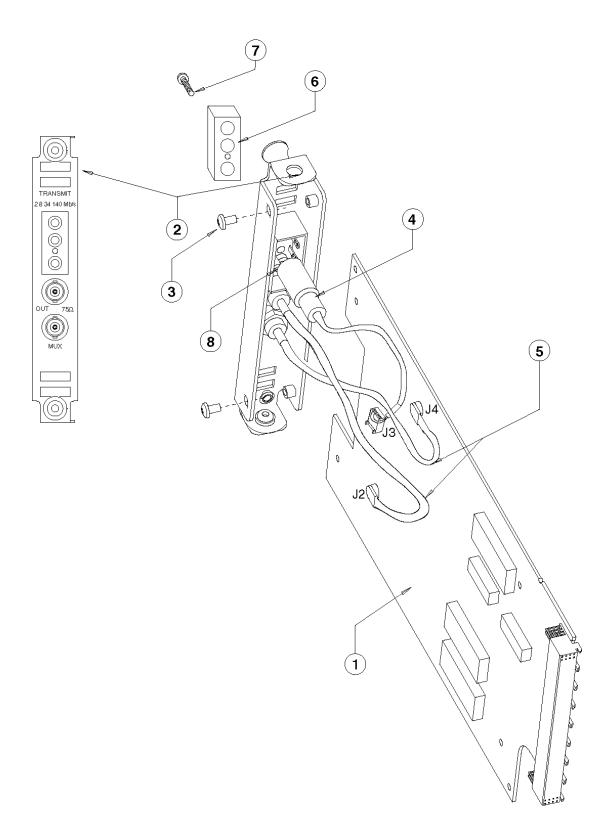

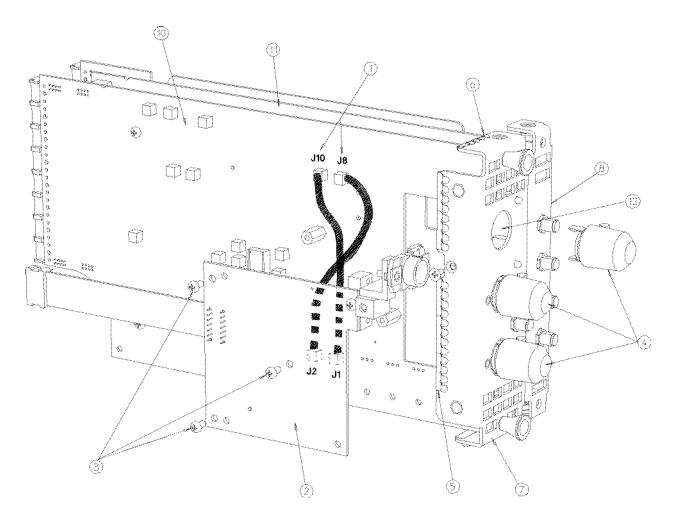

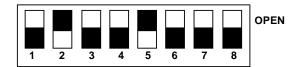

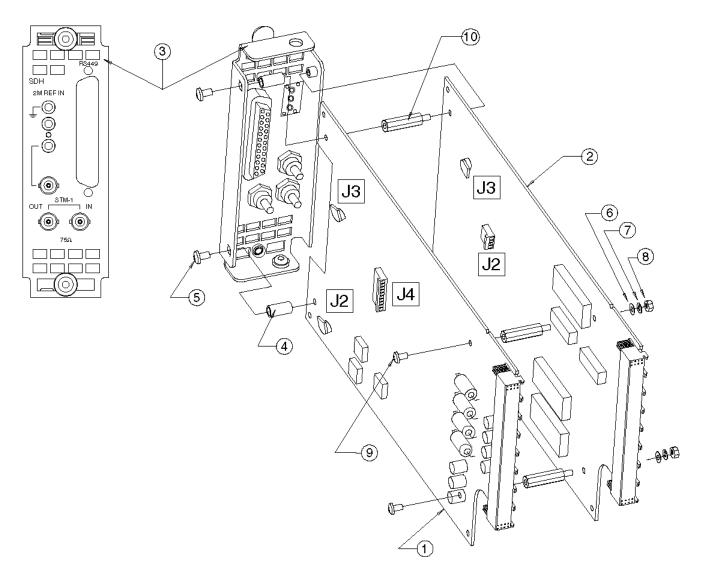

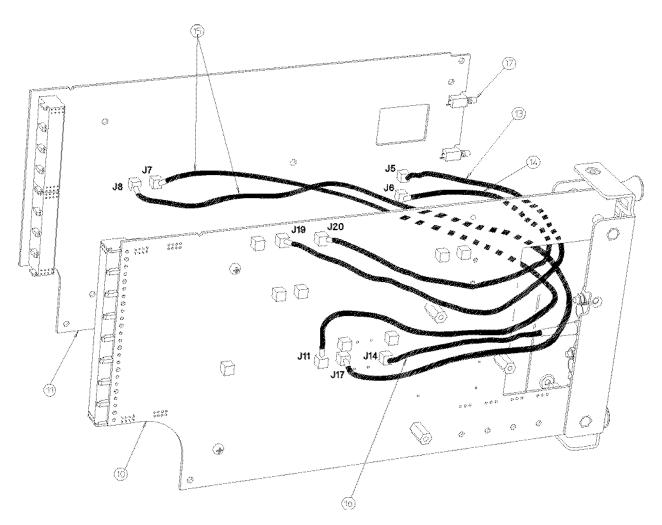

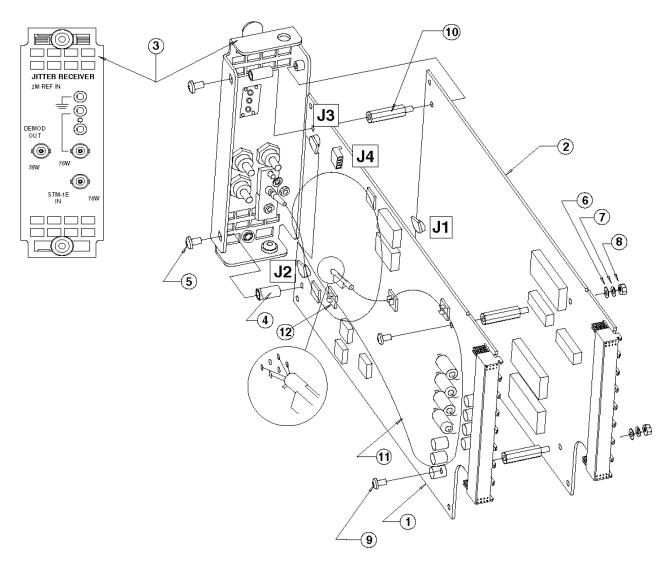

Figure 3-2 UPDH Module (topside) Adjustable Components

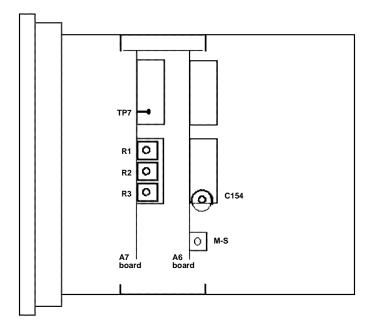

Figure 3-3 UPDH Module (underside) Adjustable Components

### CMI Pulse Amplitude

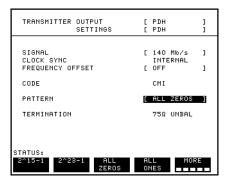

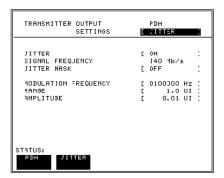

- 1 Recall the HP 37717C Default settings with the following key sequence:

Press OTHER, STORED SETTINGS Set the STORED SETTING NUMBER to 0 and set ACTION to RECALL.

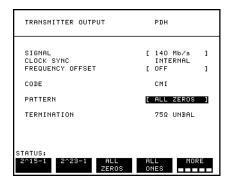

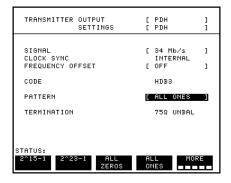

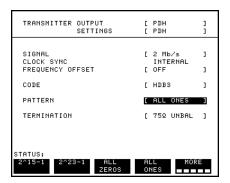

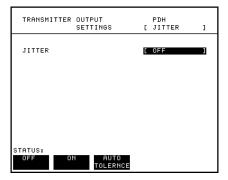

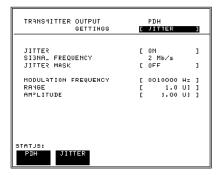

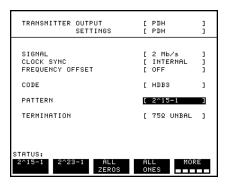

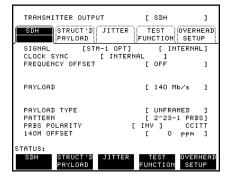

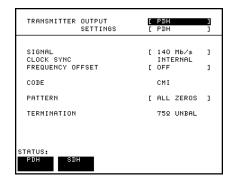

- 2 Press (TRANSMIT) and setup the display as shown below.

- 3 Connect the HP 37717C Unbalanced 75 $\Omega$  PDH OUT port to the Oscilloscope INPUT 1 via the 75/50 $\Omega$  Matching Pad set the Oscilloscope termination to 50 $\Omega$

- **4** Set the Oscilloscope Channel 1 Probe Attenuation factor to X 2.40 (equivalent to 7.6 dB) to compensate for the Matching Pad attenuation.

- **5** Press AUTOSCALE on the Oscilloscope and adjust the timebase and Delay to display a single CMI pulse.

- **6** Using the Oscilloscope, measure the peak amplitude of this pulse.

- 7 Adjust A7R1 to obtain a maximum pulse amplitude of 1 Volt pk-pk.

### CMI Pulse Mark: Space Ratio

- 8 Using the Oscilloscope, measure the pulse Mark to Space Ratio.

- **9** Adjust A7R3 to obtain a Mark to Space Ratio of 1:1.

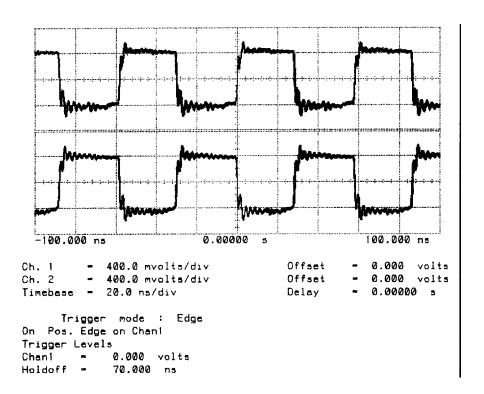

### CMI Pulse Eye-Diagram

- **10** Select PATTERN [USER WORD] [11111111000000100].

- 11 Set the Oscilloscope Timebase to 200 ps/Div and adjust the Delay to display an Eye-Diagram as shown on the next page.

- **12** Adjust A7R2 to obtain a symmetrical trace above and below the Eye Diagram cross-over point.

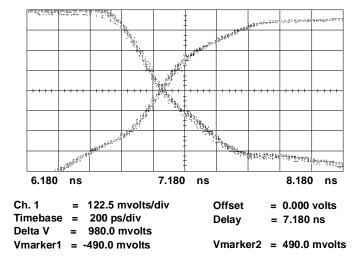

Figure 3-4 CMI Pulse Eye Diagram

### Ternary Pulse Amplitude

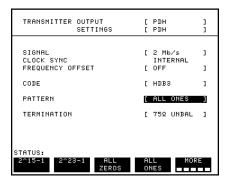

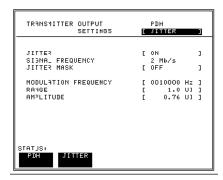

- 13 Set the BIT RATE to 704 kb/s and PATTERN to ALL ONES on the HP 37717C.

- **14** Press AUTOSCALE on the Oscilloscope and adjust the Timebase and Delay to position the positive ternary pulse in the centre of the screen.

- 15 Using the Oscilloscope, measure the peak amplitude of this pulse.

- **16** Adjust A7R4 to obtain a maximum positive pulse amplitude of 2.37 Volts.

- 17 Adjust the Oscilloscope Timebase and Delay to position the negative ternary pulse in the centre of the screen.

- 18 Using the Oscilloscope, measure the peak amplitude of this pulse.

- **19** Adjust A7R5 to obtain a maximum negative pulse amplitude of 2.37 Volts.

# **Unstructured PDH Receiver (Option UKK)**

A6 PDH Receiver Assembly.

### Adjustment Reference

| 704 kHz Recovered Clock frequency     | A6R1   |

|---------------------------------------|--------|

| 2,048 kHz Recovered Clock frequency   | A6R2   |

| 8,448 kHz Recovered Clock frequency   | A6R3   |

| 34,368 kHz Recovered Clock frequency  | A6R4   |

| 139,264 kHz Recovered Clock frequency | A6C154 |

## **Description**

A frequency counter is used to measure the recovered clock frequency at all rates. The recovered clock frequency rates are then adjusted to be within specification.

## **Equipment Required**

Extender Card HP 37714-60099

Frequency Counter HP 5335A Option 010

75 Ohm Termination HP 1522-80010

T Connector HP 1250-0781

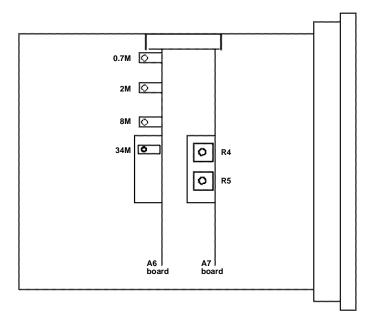

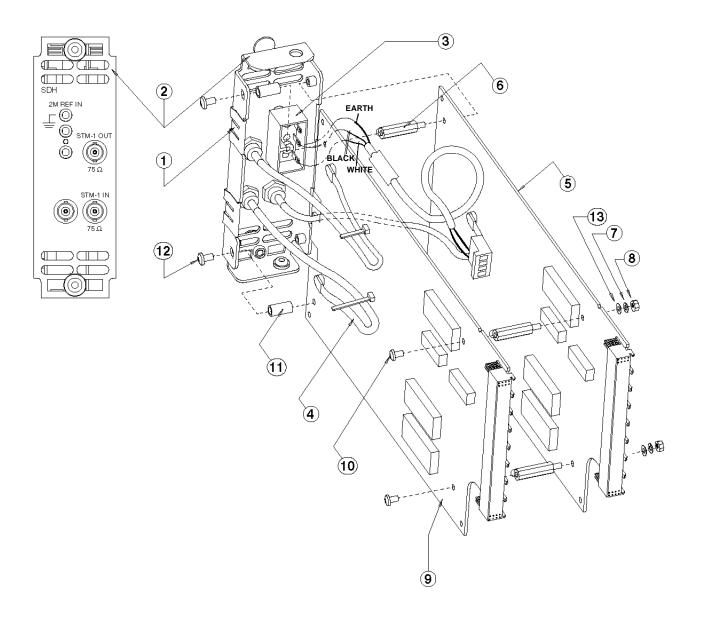

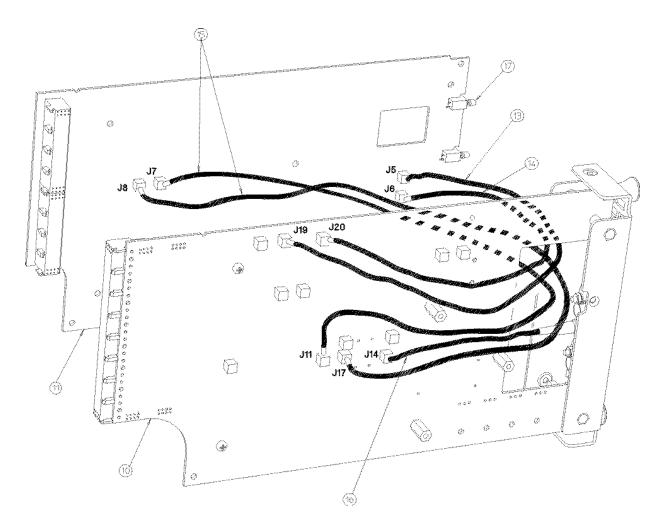

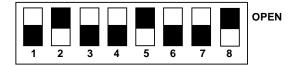

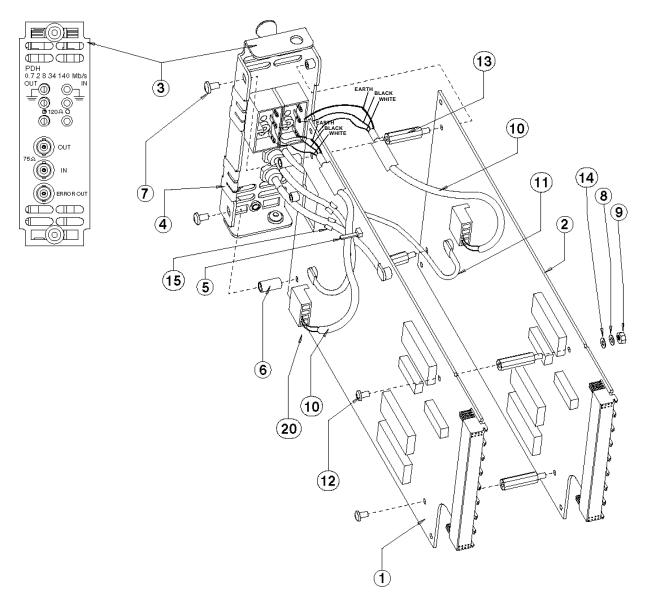

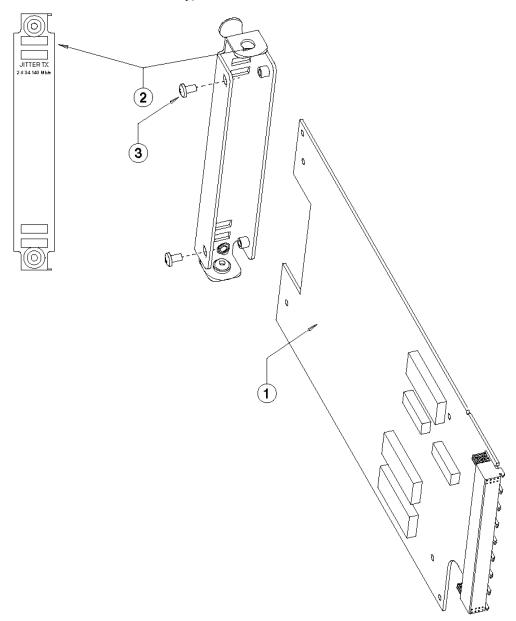

Figure 3-5 UPDH Module (topside) Adjustable Components

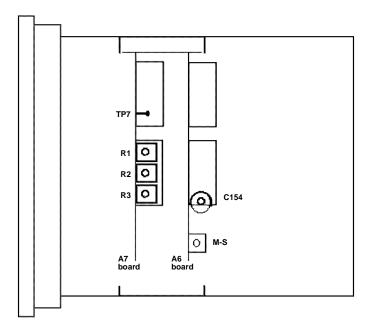

Figure 3-6 UPDH Module (underside) Adjustable Components

### 34 Mb/s Recovered Clock Frequency

- 1 Select the **CALIBRATION** function on the **OTHER** display.

- 2 Using [], DECREASE DIGIT and [], INCREASE DIGIT keys, set the CALIBRATE PASSWORD to [1243].

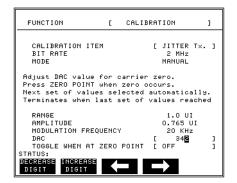

- **3** Set the CALIBRATION ITEM to CLOCK EXTRACT and SELECTED RATE to 34 Mb/s.

- 4 Press RUN/STOP

- **5** Adjust A6R4 (34M) to obtain a displayed TARGET FREQUENCY between 34,361,200 Hz and 34,374,800 Hz.

- 6 Once set, press RUN/STOP

### 140 Mb/s Recovered Clock Frequency

- 7 Set the CALIBRATION ITEM to CLOCK EXTRACT and SELECTED RATE to 140 Mb/s.

- 8 Press RUN/STOP

- **9** Adjust A6C154 (139M) to obtain a displayed TARGET FREQUENCY between 139,125,000 Hz and 139,403,000 Hz.

- 10 Once set, press RUN/STOP

### NOTE

The remaining Clock Recovery adjustments can only be performed with the PDH Module fitted on a special extender card. When removing the Module to use the Extender Card, you MUST follow the Module Removal and Replacement procedure given in the Service Section of this manual.

#### 704 kb/s Recovered Clock Frequency

- 11 Remove the PDH Module (see NOTE above), fit the Extender Card into the A6 slot in the Mainframe, then plug the A6 Assembly onto the Extender Card.

- **12** Set the CALIBRATION ITEM to CLOCK EXTRACT and SELECTED RATE to 704 kb/s.

- 13 Press RUN/STOP

- **14** Adjust A6R1 (0.7M) to obtain a displayed TARGET FREQUENCY between 703,860 Hz and 704,140 Hz.

- 15 Once set, press RUN/STOP

### 2 Mb/s Recovered Clock Frequency

- **16** Set the CALIBRATION ITEM to CLOCK EXTRACT and SELECTED RATE to 2 Mb/s.

- 17 Press RUN/STOP

- **18** Adjust A6R2 (2M) to obtain a displayed TARGET FREQUENCY between 2,047,590 Hz and 2,048,410 Hz.

- 19 Once set, press RUN/STOP

#### 8 Mb/s Recovered Clock Frequency

- ${\bf 20}~{\rm Set}$  the CALIBRATION ITEM to CLOCK EXTRACT and SELECTED RATE to  ${\bf 8}~{\rm Mb/s}.$

- 21 Press RUN/STOP

- **22** Adjust A6R3 (8M) to obtain a displayed TARGET FREQUENCY between 8,446,310 Hz and 8.449.690 Hz.

- 23 Once set, press RUN/STOP

## SDH Transmitter (Options US1 and AIT)

A9 SDH Assembly.

## Adjustment Reference

|                                  | US1  | A1T   |

|----------------------------------|------|-------|

| CMI ZEROS Pulse Mark:Space Ratio | A9R1 | A9R53 |

| CMI ONES Pulse Mark:Space Ratio  | A9R2 | A9R38 |

| CMI Tx Pulse Amplitude           | A9R3 | A9R22 |

## **Description**

An Oscilloscope is connected to the Data Output port and A9R1 and R2 are adjusted to optimize the displayed CMI pulse Mark to Space Ratio on both All Zeroes and All Ones Patterns. The pulse Amplitude is measured on the Oscilloscope and set using R3.

### **Equipment Required**

Oscilloscope HP 54520A  $75/50\Omega$  Matching Pad HP 11852B

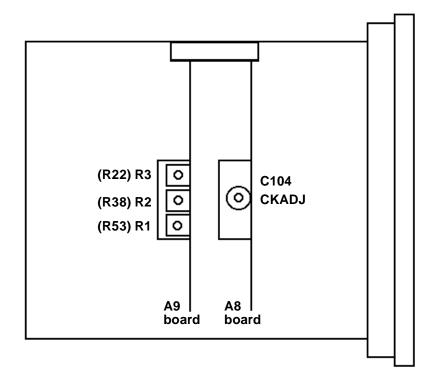

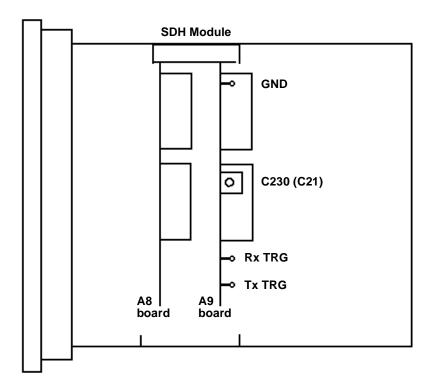

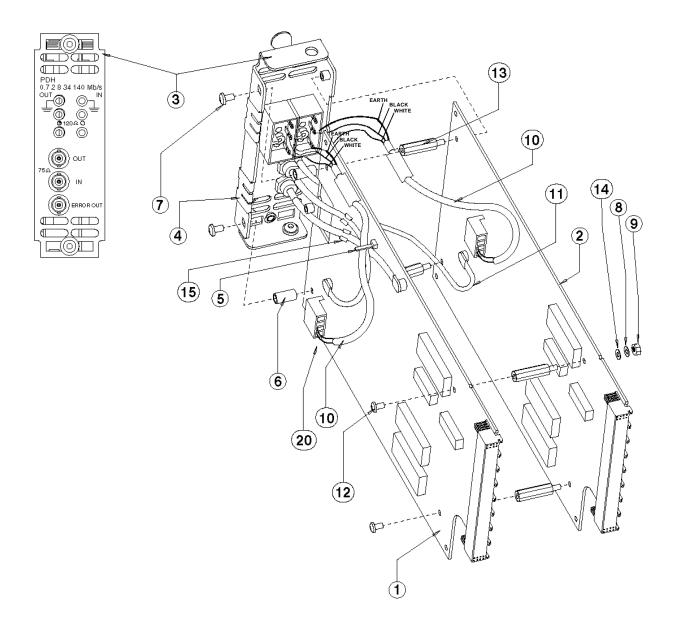

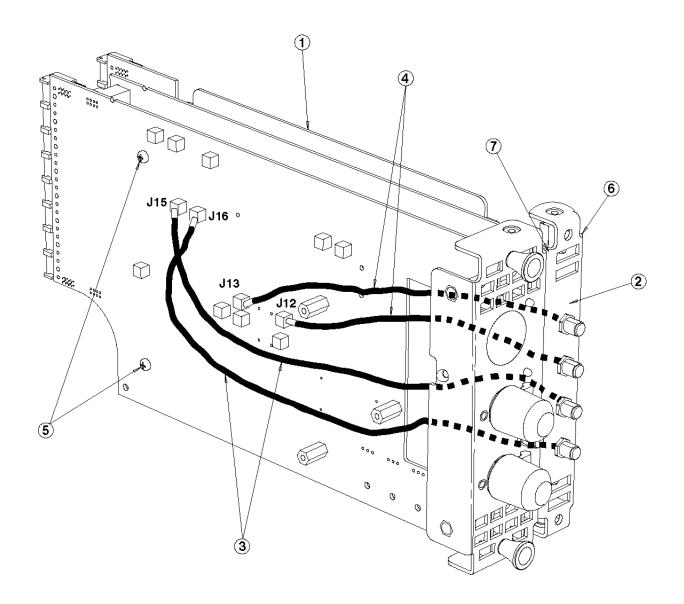

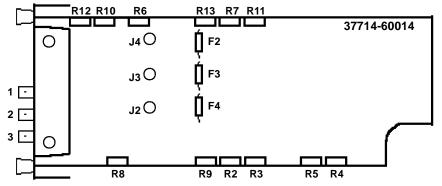

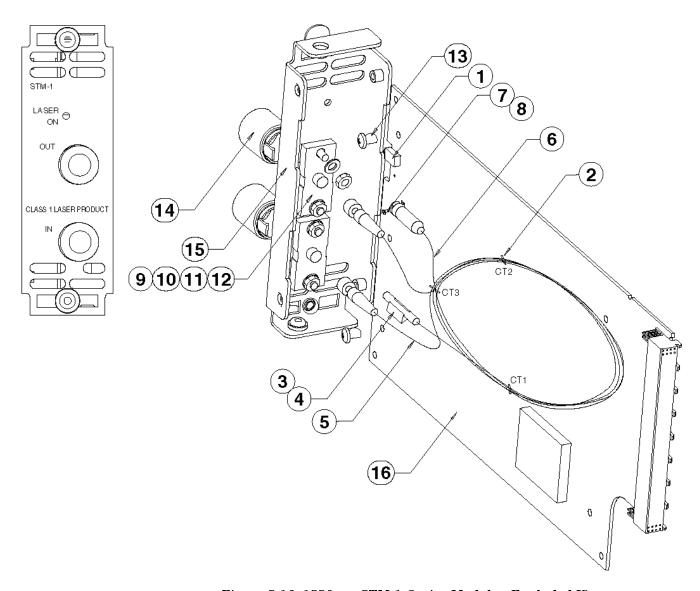

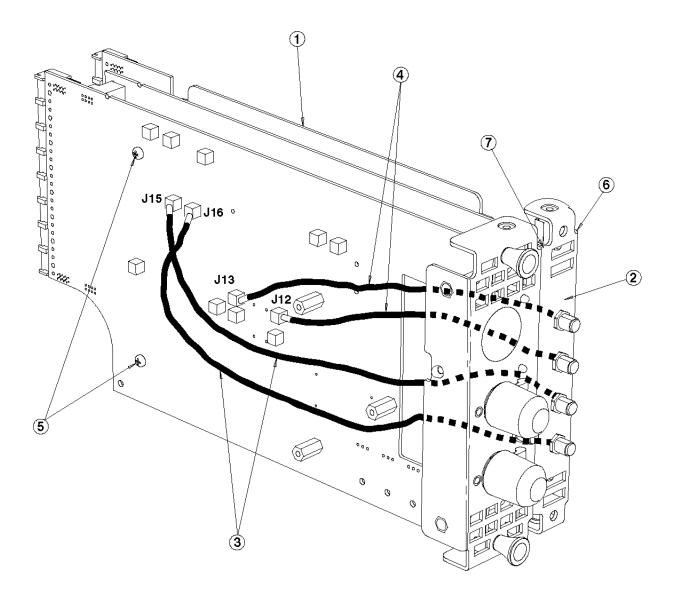

Figure 3-7 SDH Module (topside) Adjustable Components

### **CMI Pulse Amplitude**

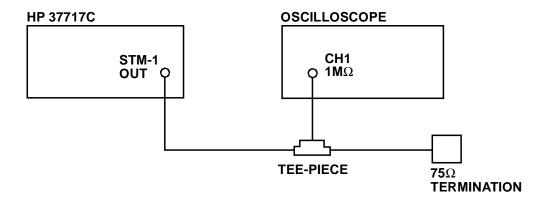

1 Connect up the equipment as shown below.

Figure 3-8 STM-1 Transmitter Output Waveshape, Test Setup

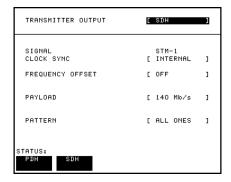

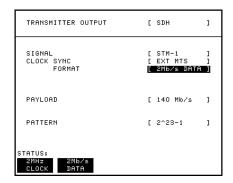

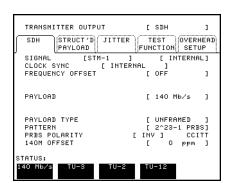

**2** Press (TRANSMIT) and set up the display as shown below.

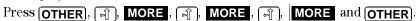

3 Make the following key sequence on the HP 37717C to obtain the special MODULE DEBUG display.

Press MORE until MODULE DEBUG appears in the softkey menu. Press MODULE DEBUG and set up the display as shown below.

FUNCTION [ MODULE DEBUG ]

MODULE [ SDH MODULE ]

DOWNLOAD LCA DESIGN [ . . ]

INTO H/W SITE NUMBER [ . . ]

TOGGLE TO DOWNLOAD TO ACTION [ OFF ]

STM-1 TEST PATTERN [ RLL ONES]

TU ASIC REGISTER [ 0000 ]

IMAGE 0101010101010101

ODL ( ODL\_GEN ) TXFRM ( TPAT )

RXFRM ( RPRSS ) BKGND ( BLANK\_42 )

RXMAP ( DMP\_139 ) DISCRIM ( STF\_139 )

TXPAT ( BLANK\_42 )

STATUS:

OFF ALL ONES

ALL ONES

STATUS:

OFF ALL ONES

### CAUTION

When using the MODULE DEBUG display, ONLY modify the STM-1 TEST PATTERN. Altering other parameters can damage instrument firmware - exit this display after setup to eliminate any possibility of accidental modification.

- **4** Set the Oscilloscope Channel 1 Probe Attenuation factor to X 2.40 (equivalent to 7.6 dB) to compensate for the Matching Pad attenuation.

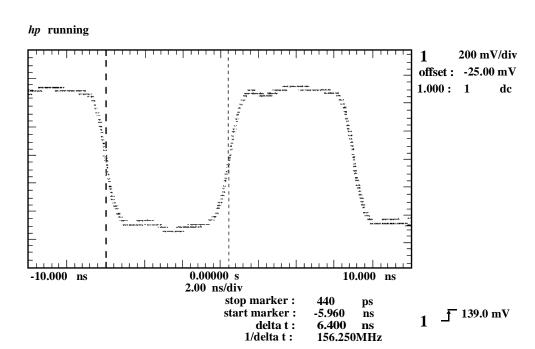

- **5** Press AUTOSCALE on the Oscilloscope and adjust the timebase and Delay to display a CMI pulse as shown below.

- **6** Using the Oscilloscope, measure the pulse amplitude at the half-width point.

- 7 Adjust A9R3, R22 to obtain a pulse amplitude of 1 Volt pk-pk.

8 STM-1 All Ones Pattern

### CMI All Ones Pulse Mark: Space Ratio

- **9** Using the Oscilloscope, measure the pulse Mark to Space Ratio.

- **10** Adjust A9R2, R38 to obtain a Mark to Space Ratio of 1:1.

### CMI All Zeros Pulse Mark: Space Ratio

- **11** Set the STM-1 TEST PATTERN to ALL ZEROS on the HP 37717C MODULE DEBUG display.

- 12 Using the Oscilloscope, measure the pulse Mark to Space Ratio.

- 13 Adjust A9 R1, R53 to obtain a Mark to Space Ratio of 1:1.

- **14** Repeat steps 8 to 12 until no further adjustment is required.

## **SDH Receiver (Option AIT)**

A9 SDH Assembly.

## Adjustment Reference

155.52 MHz Recovered Clock frequency A9C230

## **Description**

A Frequency Counter is connected to the Recovered Clock Oscillator output Probe Point and A9C230, C21 is adjusted to bring the clock free-run frequency within specified limits.

## **Equipment Required**

Frequency Counter HP 5335A Opt 001

10:1 Oscilloscope Probe HP 10435A

Extender Card HP 37714-60099

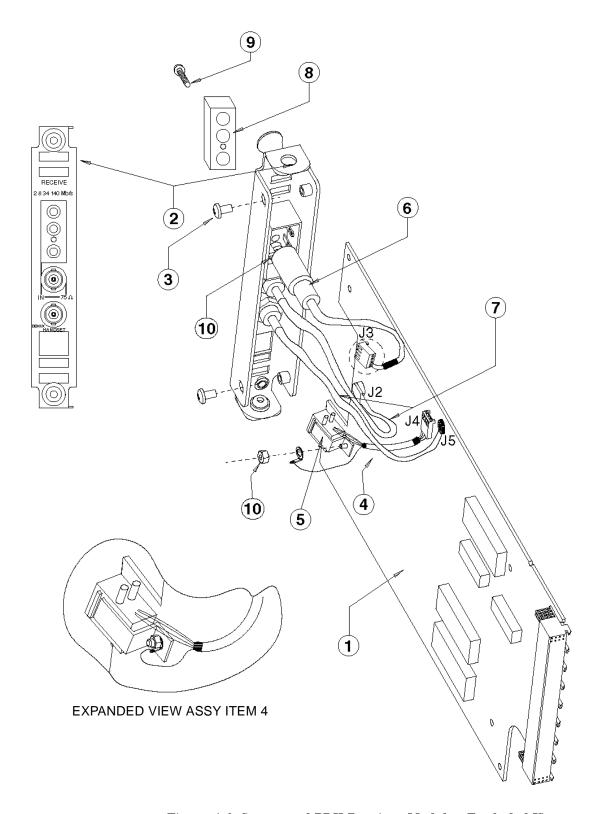

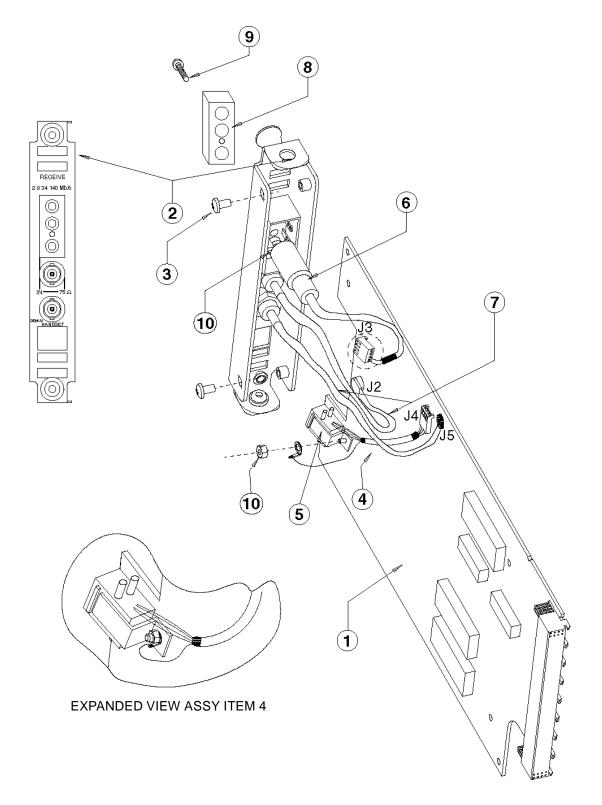

Figure 3-9 SDH Module (underside) Adjustable Components

### NOTE

The probe points for this adjustment can only be accessed with the SDH Module fitted on a special Extender Card. When removing the Module to use the Extender Card, you MUST follow the procedure in Module Removal and Replacement given in the Service Section of this manual.

### 155.52 MHz Recovered Clock Frequency

- 1 Remove the SDH Module (see NOTE above), fit the Extender Card into the A9 slot in the Mainframe, then plug the A9 Assembly onto the Extender Card.

- **2** Select Frequency A and  $1M\Omega$  input impedance on the Frequency Counter.

- 3 Connect the Frequency Counter Input A to probe point E6 on the A9 Assembly using the 10:1 probe (ground the probe on the pad beside E6).

- **4** Adjust A9C230, C21 to obtain a reading on the Counter between 154,520,000 Hz and 156,520,000 Hz.

- **5** Disconnect all test equipment.

## External Clock (Option A1T)

A8 Offset Clock Assembly.

## Adjustment Reference Offset Clock Assembly.

External MTS Recovered Clock frequency A8C104 (CK ADJ)

## **Description**

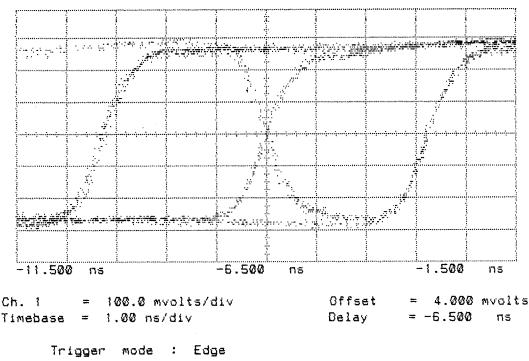

A 2 MB/s PRBS Data signal from the HP 37717C Communications Performance Analyzer is applied to the External MTS Reference port on the HP 37717C. The Recovered Clock frequency is optimized by monitoring the clock oscillator output on an Oscilloscope and adjusting A8C104 to minimize the displayed jitter.

## **Equipment Required**

Digital Transmission Test Set HP 37717C

Oscilloscope HP 54520A

10:1 Oscilloscope Probe HP 10435A

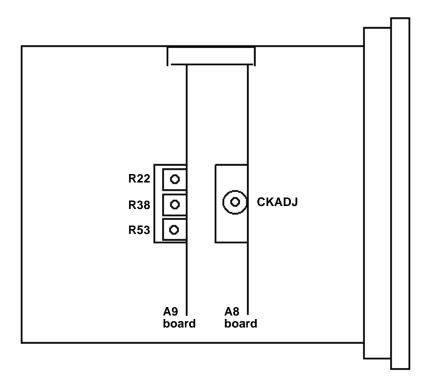

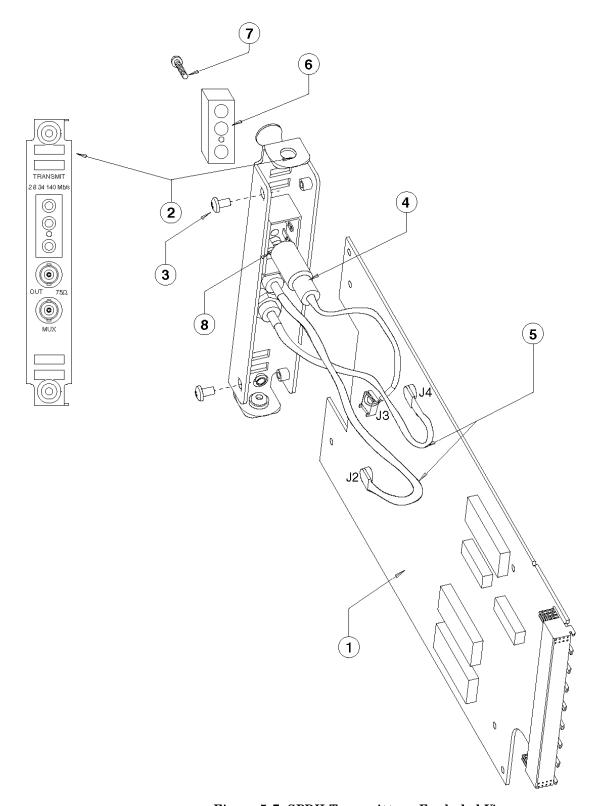

Figure 3-10 SDH Module (topside) Adjustable Components

### **External MTS Recovered Clock Frequency**

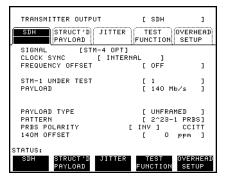

1 Set the HP 37717C as follows:

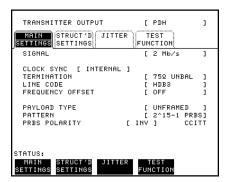

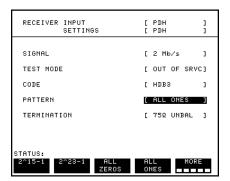

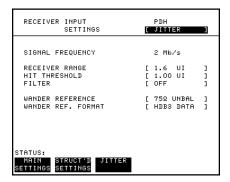

2 Set the Test Set as shown and connect the 2 Mb/s output to the External MTS Clock IN  $75\Omega$  Unbalanced port on the HP 37717C SDH module.

- 3 Connect the Oscilloscope Probe to TP3 (Clock Out) on the A8 Assembly using the 10:1 probe (ensure probe is properly grounded). TP3 is accessible through a slot in the bottom of the instrument.

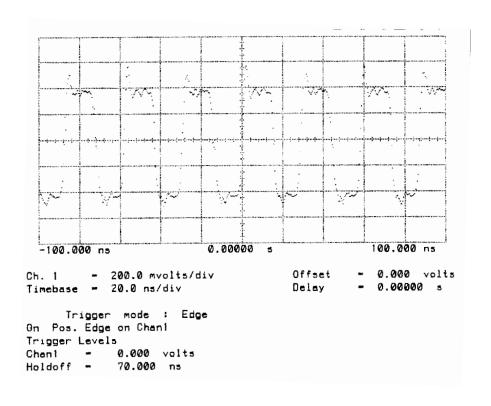

- **4** Press AUTOSCALE on the Oscilloscope and adjust the Timebase and Delay to display a waveform similar to that shown on Page 3-24 in Figure 3-11.

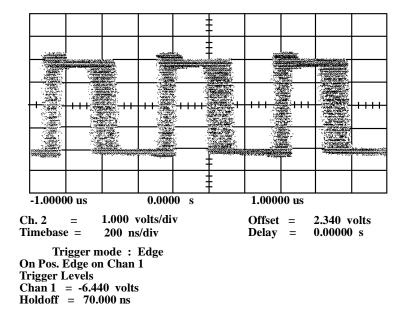

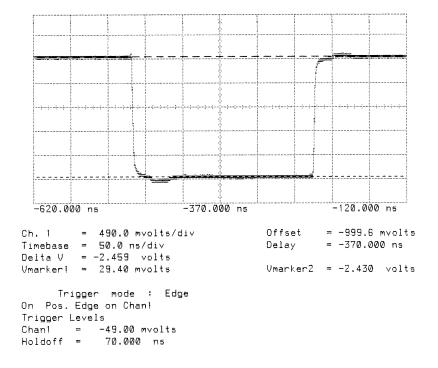

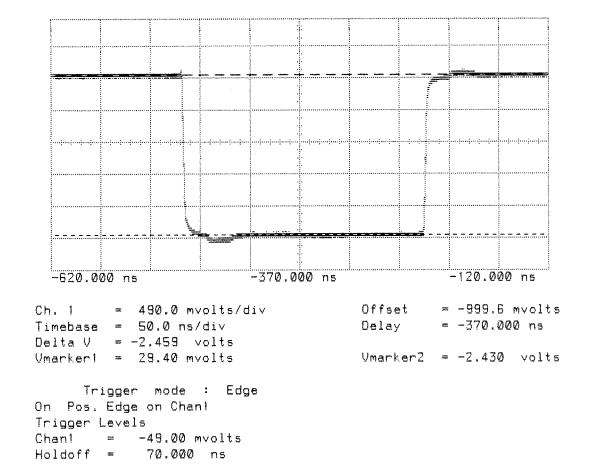

Figure 3-11 External MTS Clock Minimum Jitter Adjustment

- **5** Adjust A8C104 (CKADJ) to obtain minimum jitter on the displayed waveform.

- 6 Disconnect all test equipment.

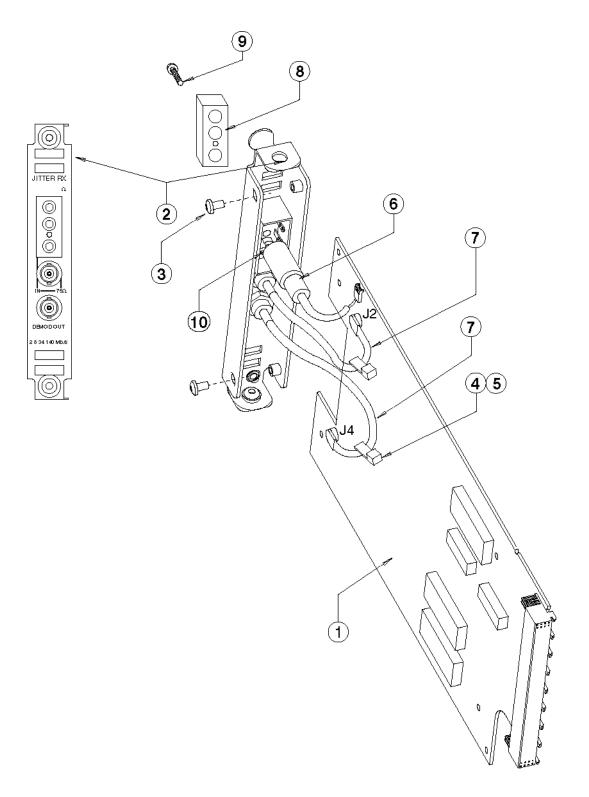

# 1310 nm STM-1 Optical Transmitter (Option UH1 Only)

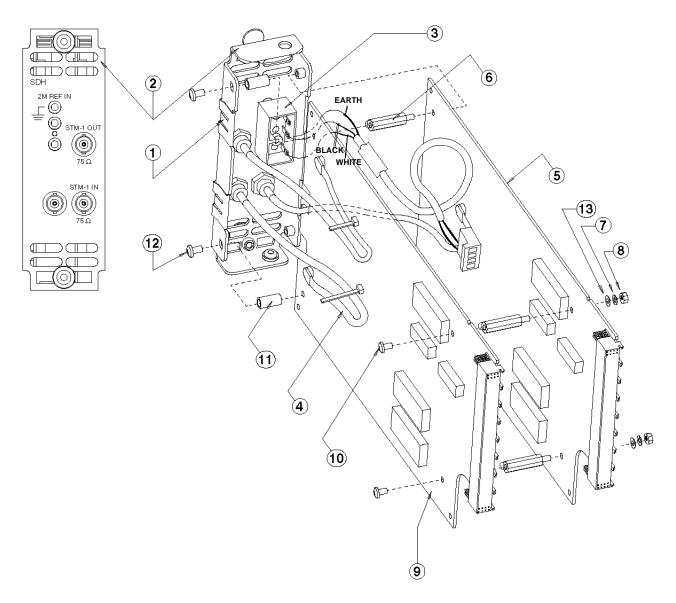

A11 Optical Assembly.

## Adjustment Reference

Optical Tx Power Output Level A11 R1

## **Description**

An Optical Power Meter is connected to the output of the 155 Mb/s Optical Transmitter and the power output is adjusted to the correct level using A11R1.

## **Equipment Required**

| Power Meter                 | HP 8153A       |

|-----------------------------|----------------|

| Power Meter Sensor Module   | HP 81536A      |

| FC/PC Connector Interface   | HP 81000F1     |

| Optical Cables (quantity 2) | HP 11871A      |

| Extender Card               | HP 37714-60099 |

Figure 3-12 STM-1 Adjustable Components